Grid and formation of fast-flashing memory therewith

A memory and gate technology, which is applied in the field of gate and flash memory formation, can solve problems such as complex processes, and achieve the effects of increasing gate width, avoiding corners, and preventing erosion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

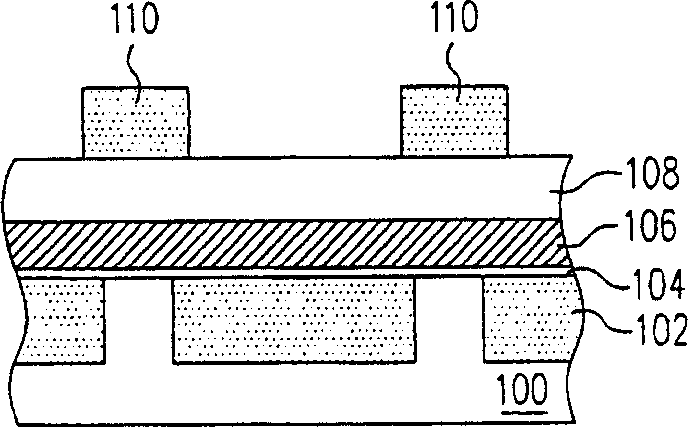

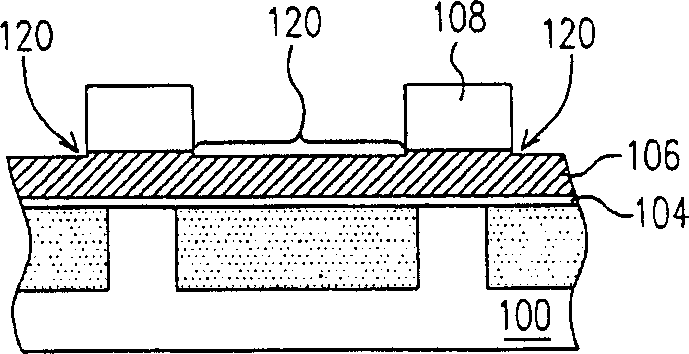

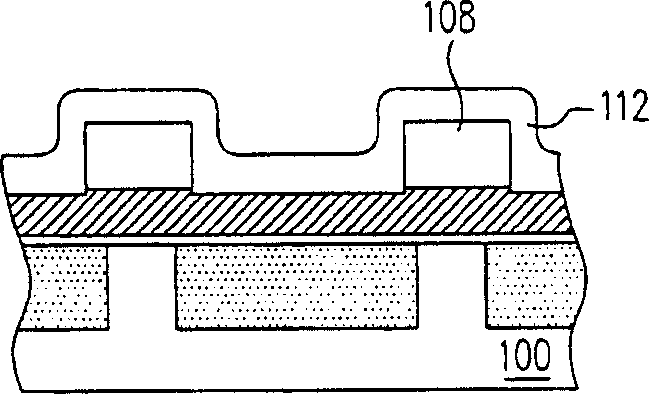

[0045] Figure 3A to Figure 3F is a schematic cross-sectional view of the manufacturing process of the gate according to a preferred embodiment of the present invention. Please refer to Figure 3A , a substrate 300 is provided, on which a gate dielectric layer 304 has been formed, and an isolation structure 302, such as a shallow trench isolation structure (STI), is provided in the substrate 300 . Then, a conductive layer 306 is formed on the gate dielectric layer 304, and its material is, for example, a doped polysilicon layer or other suitable materials. Next, an isolation protection layer 320 is formed on the conductor layer 306, such as a silicon oxide layer formed using tetraethoxysilane (TEOS) as a reactive gas source, and the method for forming this isolation protection layer 320 is, for example, low pressure chemical vapor deposition method. Afterwards, a sacrificial layer 308 is formed on the isolation protection layer 320 , wherein the sacrificial layer 308 is, fo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More