Non-volatile semiconductor memory device

A storage device, non-volatile technology, used in semiconductor devices, semiconductor/solid-state device manufacturing, read-only memory, etc., can solve problems such as insufficient data "0" writing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

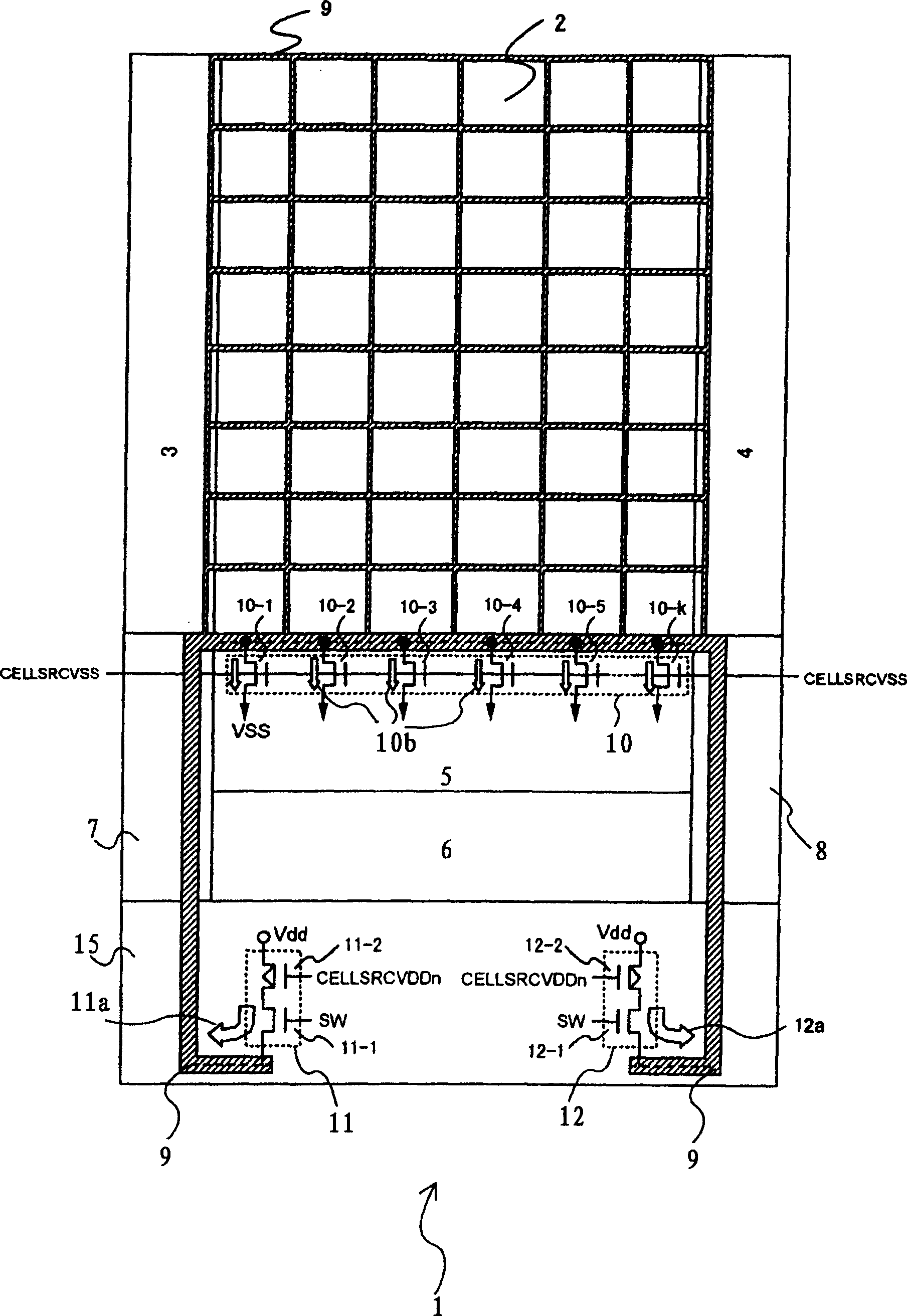

[0097] In this embodiment, an example in which charging cell source line drivers 11 and 12 are arranged on intersections 7 and 8 in NAND flash memory 1 of the present invention described in the above embodiments will be described.

[0098] refer to Figure 5 . Figure 5 A schematic configuration diagram of the NAND-type flash memory 20 of the present invention according to the present embodiment is shown. right in Figure 5 In the NAND type flash memory 20 according to the present invention shown in this embodiment, the same configuration as that of the NAND type flash memory 1 of the present invention described in the above-mentioned embodiment is given the same reference numerals, so it will not be omitted here. Let me explain.

[0099] Such as Figure 5 As shown, in the NAND flash memory 20 of this embodiment, the cell source line drivers 11 and 12 for charging are disposed on the intersection portion 7 and the intersection portion 8, respectively. In this way, the wir...

Embodiment 2

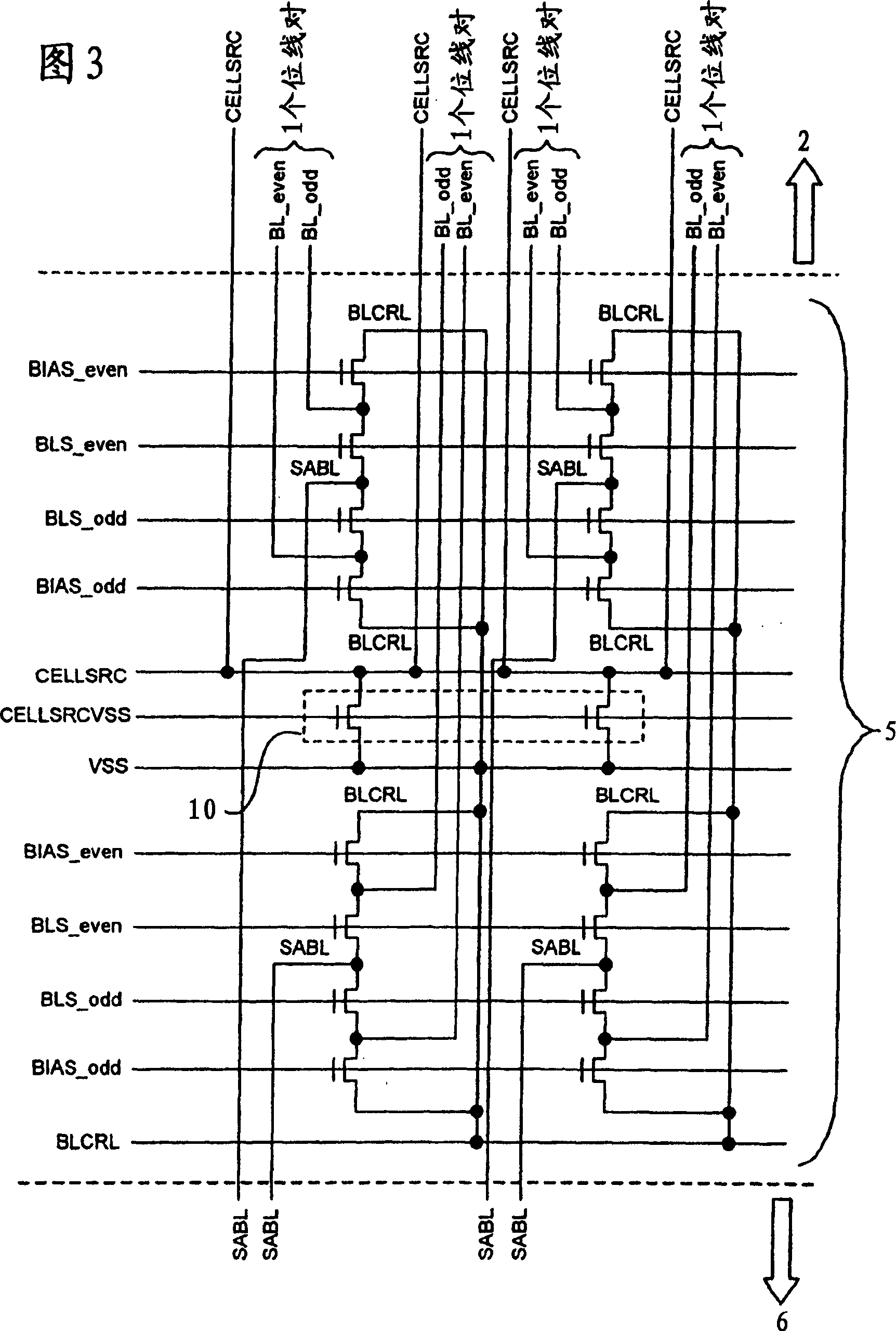

[0101] In this embodiment, in the NAND flash memory 1 of the present invention described in the above-mentioned embodiments, the cell source line (CELLSRC) is arranged in the high-voltage transistor region of the sense amplifier portion next to the cell array. An example of a transistor whose potential is equalized with that of the bit line shield line (BLCRL).

[0102] refer to Figure 6 . Figure 6 A schematic configuration diagram of the NAND-type flash memory 30 of the present invention according to the present embodiment is shown. right in Figure 6 In the NAND type flash memory 30 according to the present invention shown in this embodiment, the same configuration as that of the NAND type flash memory 1 of the present invention described in the above-mentioned embodiment is given the same reference numerals, so it will not be omitted here. Let me explain.

[0103] In the NAND flash memory 30 of this embodiment, the potential of the cell source line (CELLSRC) and the p...

Embodiment 3

[0116] This embodiment describes an example in which charging cell source line drivers 11 and 12 are arranged on intersections 7 and 8, respectively, in NAND flash memory 30 of the present invention described in Embodiment 2 above.

[0117] refer to Figure 12 . Figure 12 A schematic configuration diagram of the NAND type flash memory 40 of the present invention according to the present embodiment is shown. right in Figure 12 In the NAND flash memory 40 according to the present invention shown in this embodiment, the NAND flash memory 1 of the present invention and the NAND flash memory 30 of the present invention described in the above-mentioned embodiment mode and Example 2 are The same structures are given the same reference numerals, so they will not be described again here.

[0118] Such as Figure 12 As shown, in the NAND flash memory 40 of this embodiment, the cell source line drivers 11 and 12 for charging are disposed on the intersection portion 7 and the inters...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More