Controlling method for gate formation of semiconductor device

一种半导体、栅极的技术,应用在半导体装置的栅极形成控制领域,能够解决无法提供、很难完整设定等问题,达到生产量减少的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] In order to make the above objects, features and advantages of the present invention more comprehensible, a preferred embodiment will be described in detail below together with the accompanying drawings.

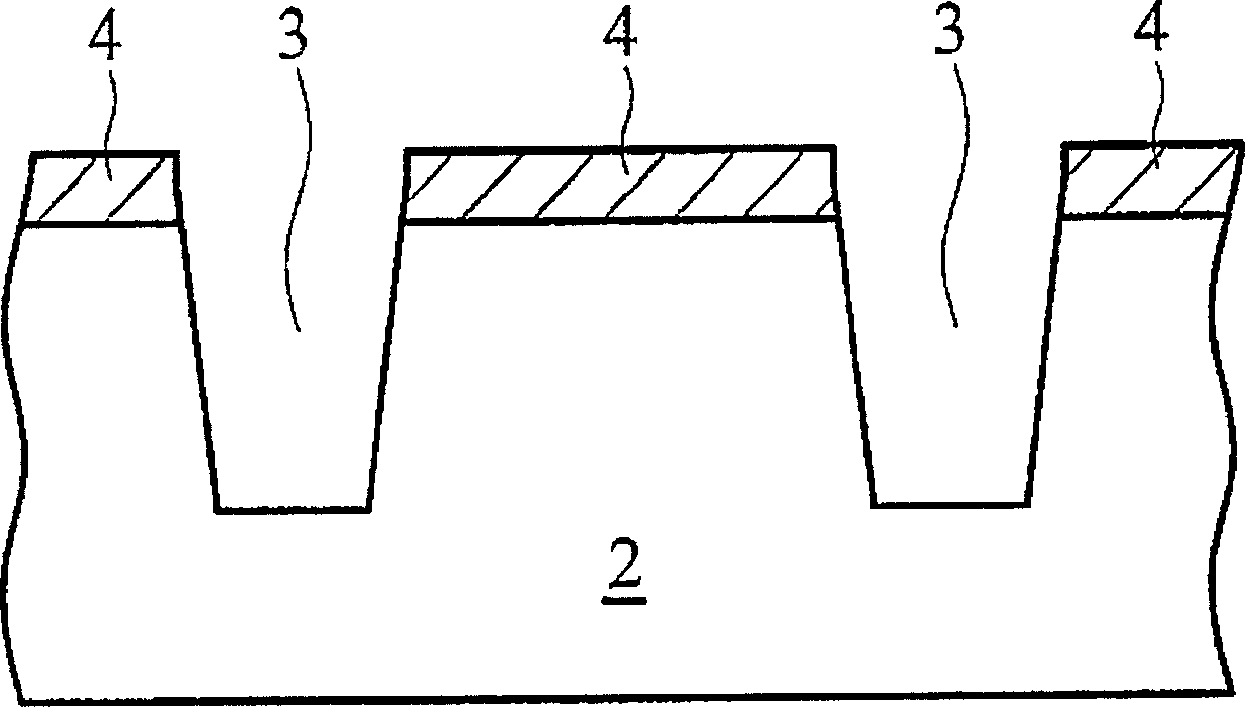

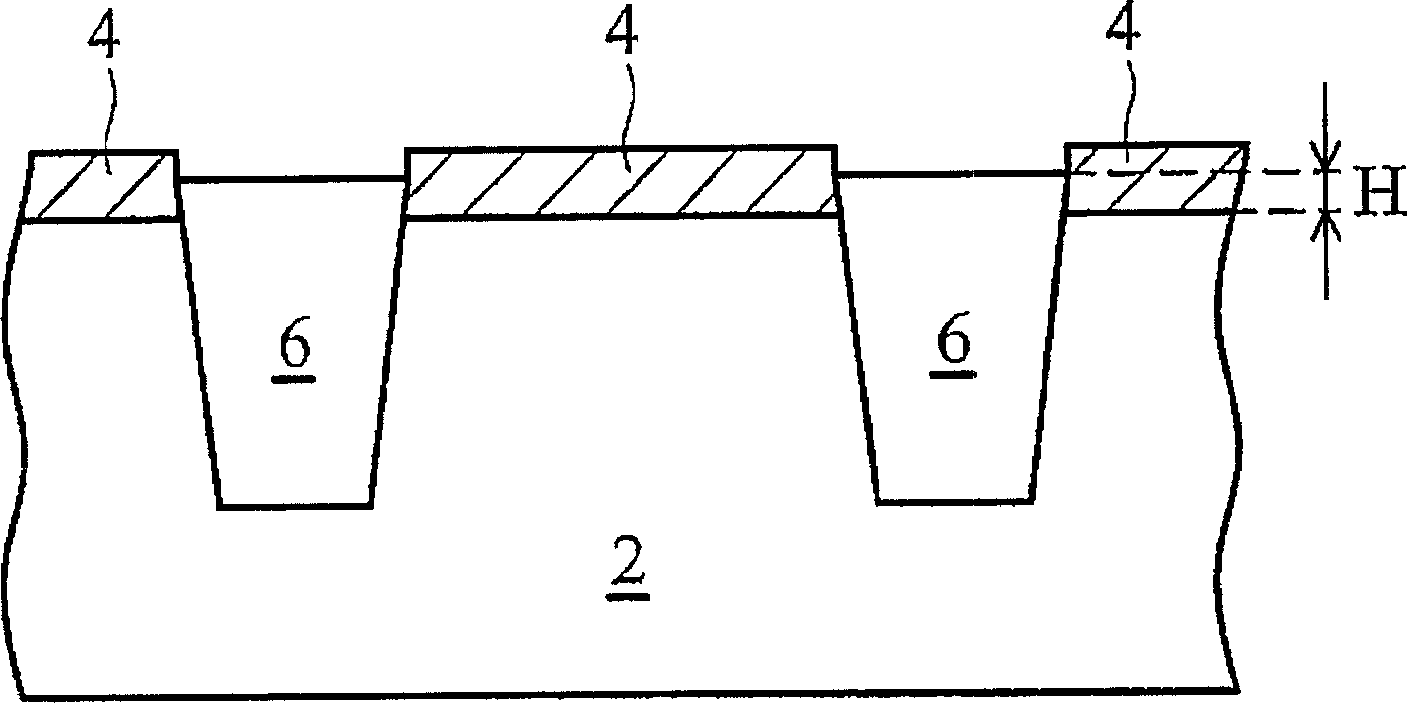

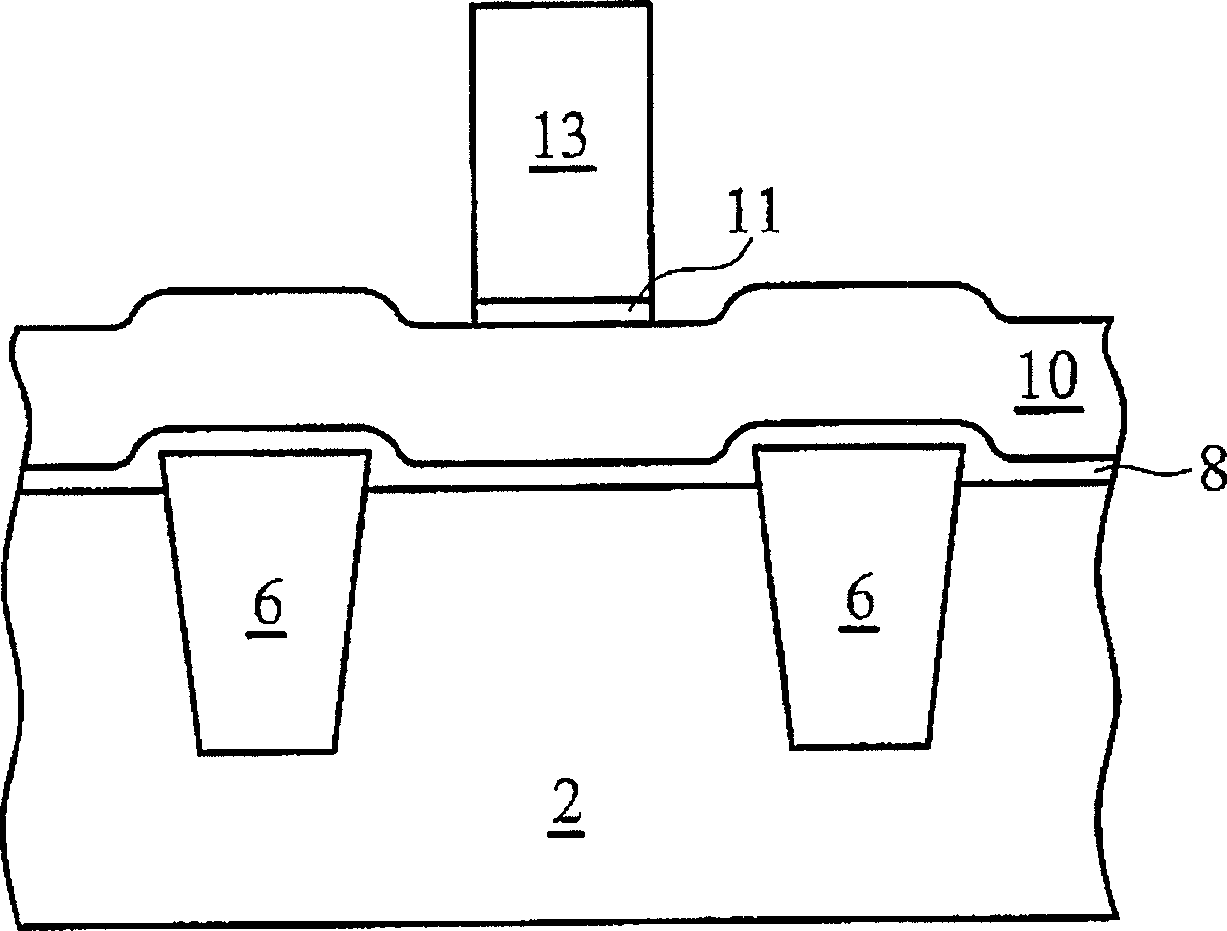

[0036] figure 1 , figure 2 , Figure 3A to Figure 3C ,as well as Figure 4It represents a general MOS device and its formation, including the formation of shallow trench isolation (Shallow Trench Isolation, STI) 6 . A mask layer 4 is formed on the active region 2 . In the provided embodiment, the mask layer 4 is formed of silicon nitride using Low Pressure Chemical Vapor Deposition (LPCVD). In other embodiments, the mask layer 4 is formed by thermal nitridation of silicon, plasma-assisted chemical vapor deposition (Plasma Enhanced Chemical Vapor Deposition, PECVD), or plasma anodic nitridation using nitrogen-hydrogen ( plasmaa nodicnitridation) to form. The channel 3 is formed by anisotropically etching into the active region 2 through the mask layer 4 or silic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com