Cobalt silicon contact barrier metal process for high density semiconductor power devices

An oxide semiconductor and metal technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve problems such as loss of dopants at the contact interface

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

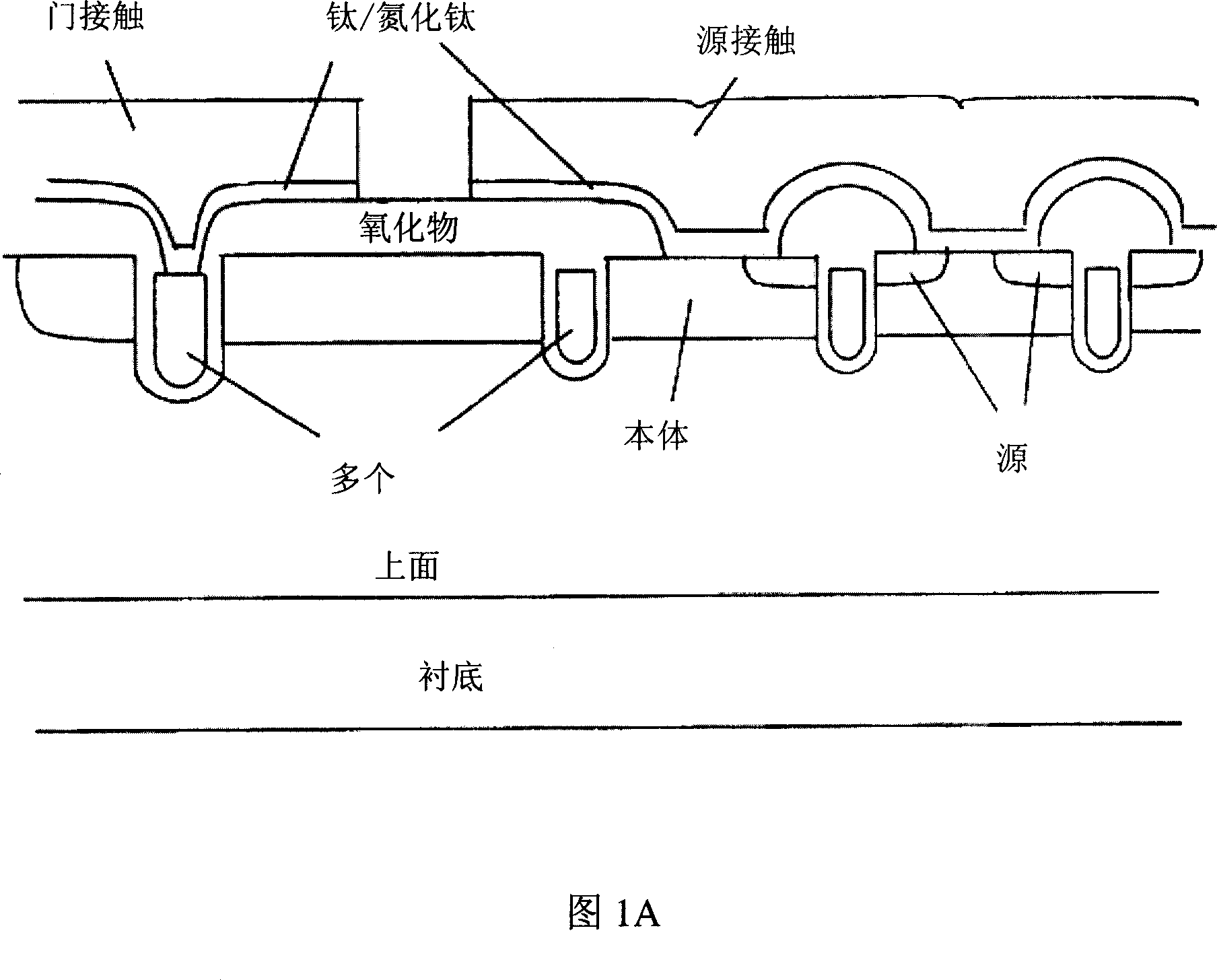

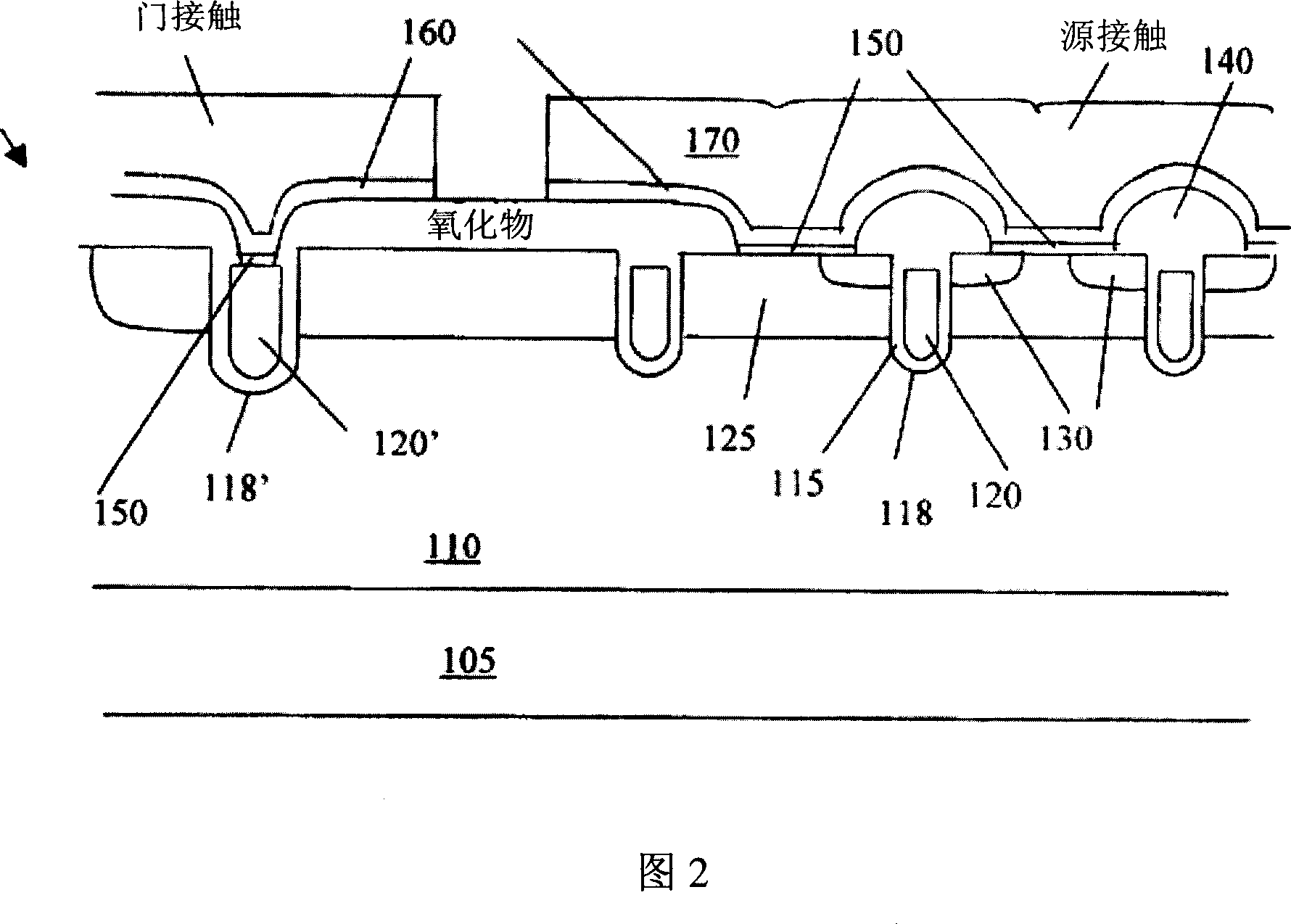

[0015] Turn now to the cross-sectional view of trench DMOS device 100 in FIG. 2 . The trench DMOS device 100 is supported on a substrate 105 including an epitaxial layer 110 and includes a trench gate 120 in a trench 118 with a gate insulating layer 115 formed over the trench walls. The body region 125 doped with a second conductivity type, such as a P-type dopant, extends between the trench gates 120, and the P-body region 125 surrounding the source region 130 adopts the first conductivity type, such as N+ doping agent doping. The active region 130 is formed around the top surface of the epitaxial layer surrounding the trench gate 120 , and the top surface of the semiconductor substrate extending to the top of the trench gate, P-body region 125 and source region 130 is covered with a dielectric capping layer 140 . Trench DMOS device 100 also includes an insulating gate runner 120' arranged in gate runner trench 118', and connected to gate 120, the connections of which are no...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More