Apparatuses for treating pluralities of discrete semiconductor substrates; and methods for treating pluralities of discrete semiconductor substrates

a technology of discrete semiconductor substrates and apparatuses, which is applied in the direction of crystal growth process, photosensitive materials, instruments, etc., can solve the problems of difficult control of reactions, and difficult to form uniform layers over multiple exposed surfaces of one or more semiconductor substrates with cvd

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

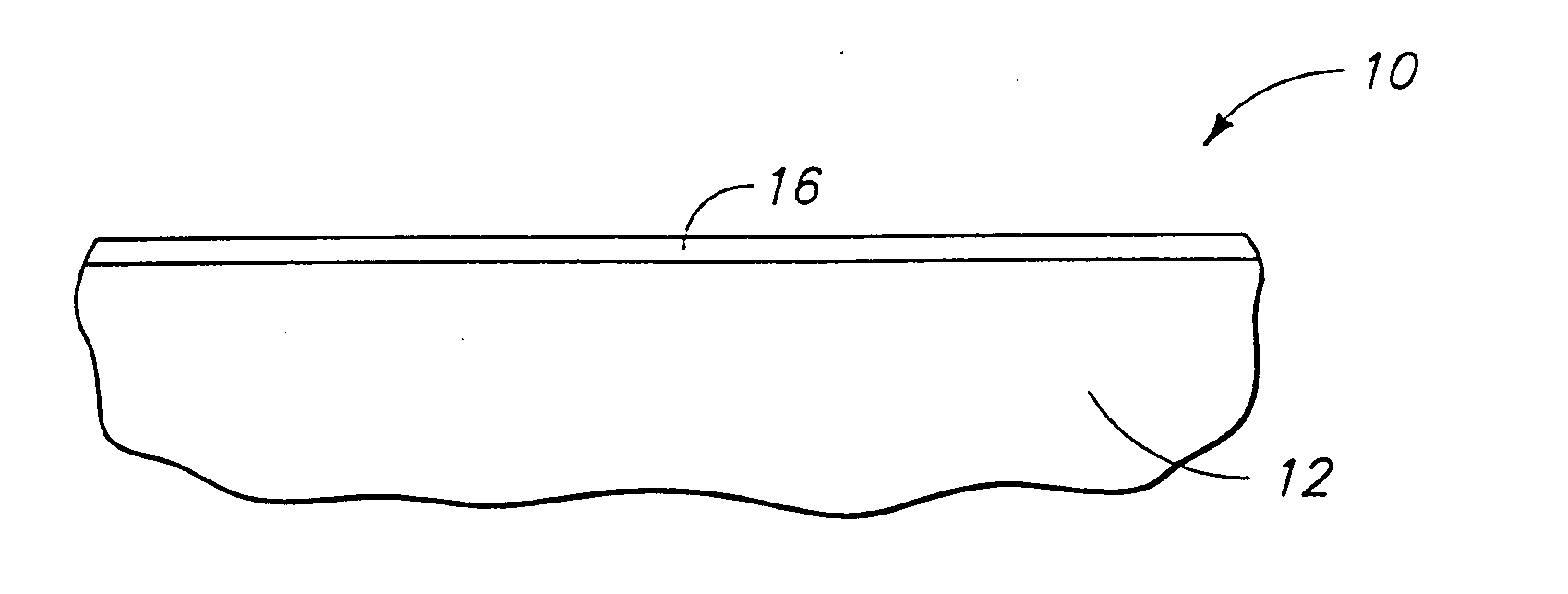

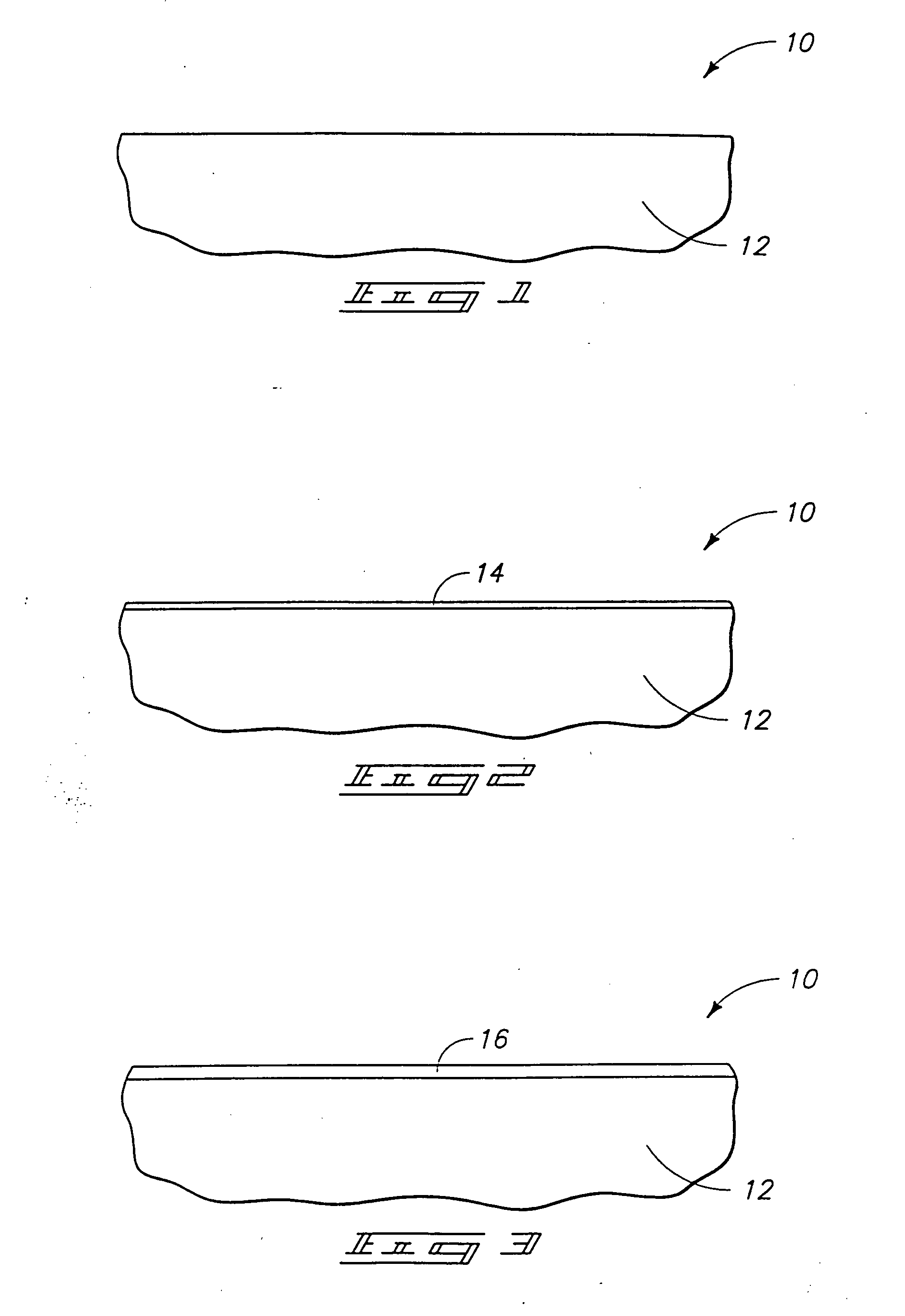

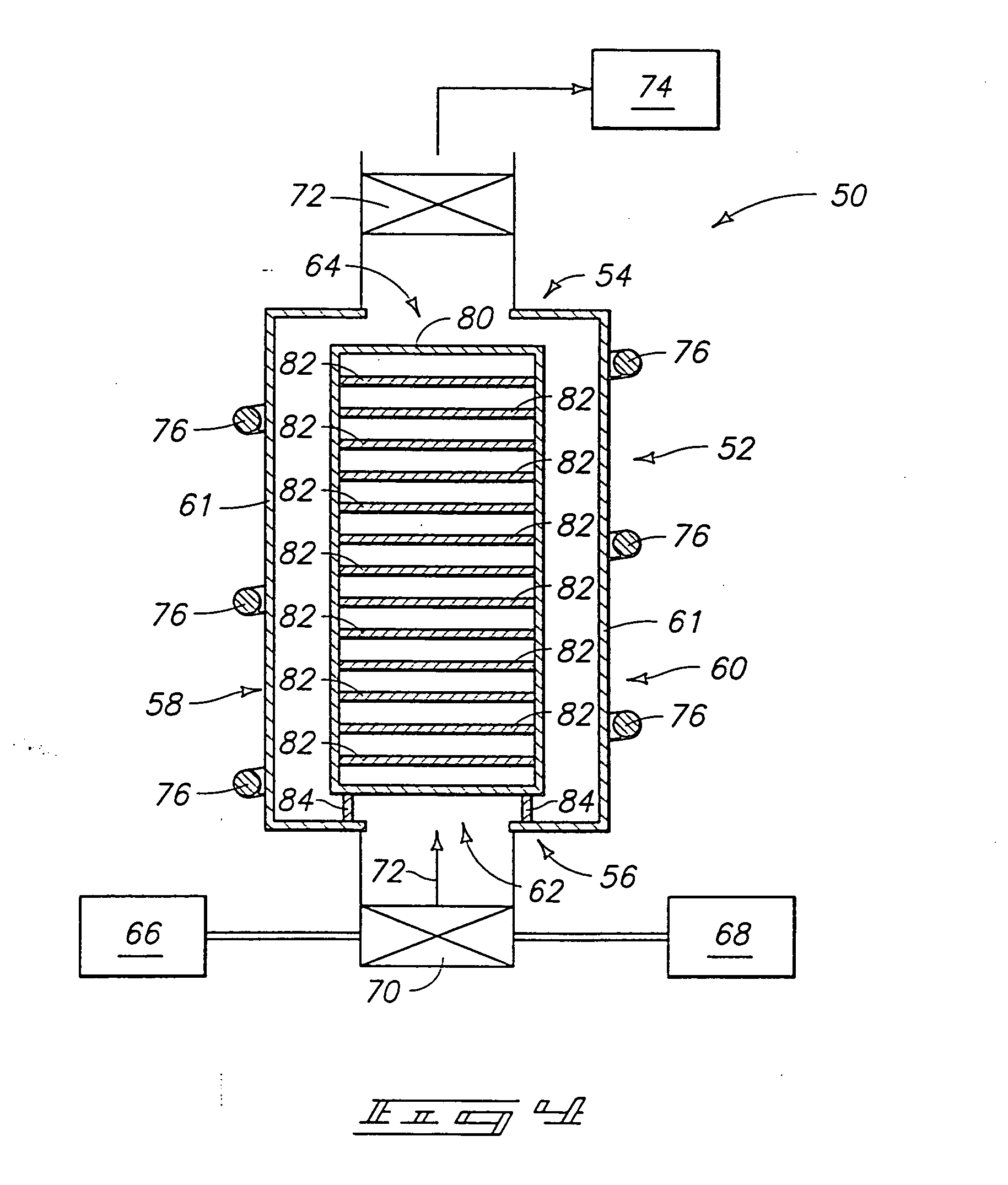

[0019] In particular aspects, the present application pertains to atomic layer deposition (ALD) technology. ALD technology typically involves formation of successive atomic layers on a substrate. Such layers may comprise, for example, an epitaxial, polycrystalline, and / or amorphous material. ALD may also be referred to as atomic layer epitaxy, atomic layer processing, etc.

[0020] The deposition methods herein are described in the context of formation of materials on one or more semiconductor substrates. In the context of this document, the term “semiconductor substrate” or “semiconductive substrate” is defined to mean any construction comprising semiconductive material, including, but not limited to, bulk semiconductive materials such as a semiconductive wafer (either alone or in assemblies comprising other materials thereon), and semiconductive material layers (either alone or in assemblies comprising other materials). The term “substrate” refers to any supporting structure, includ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Fraction | aaaaa | aaaaa |

| Fraction | aaaaa | aaaaa |

| Fraction | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More