Apparatus and method for fabricating semiconductor devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] Hereinafter, a preferred embodiment of the present invention will be described with reference to the accompanying drawings. In the following description and drawings, the same reference numerals are used to designate the same or similar components, and so repetition of the description on the same or similar components will be omitted.

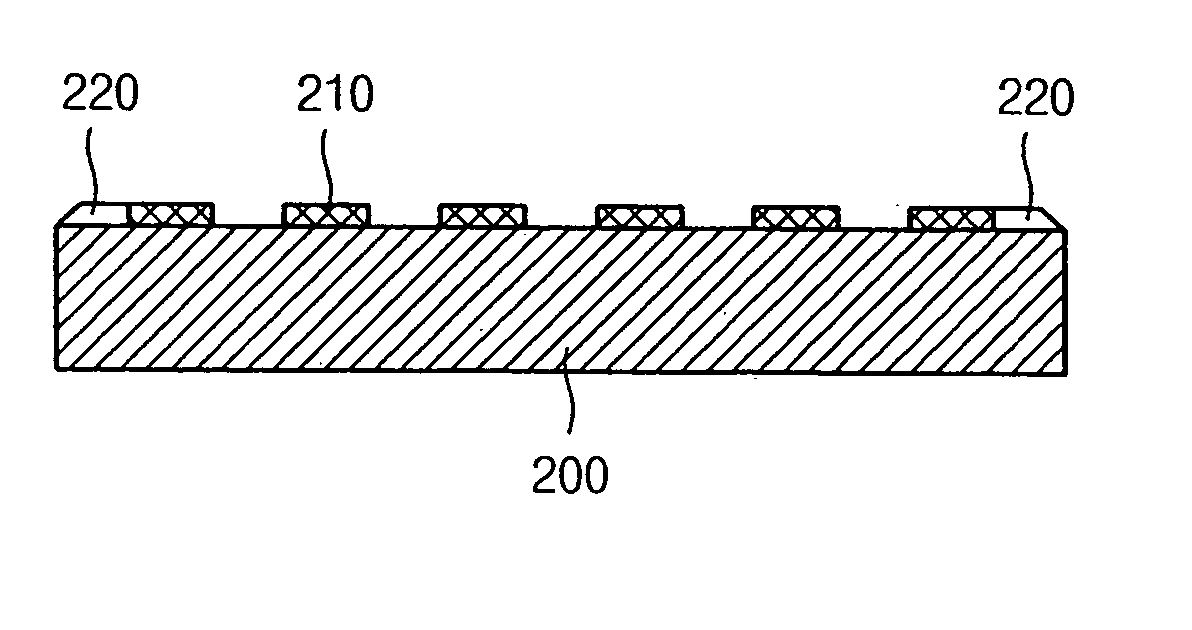

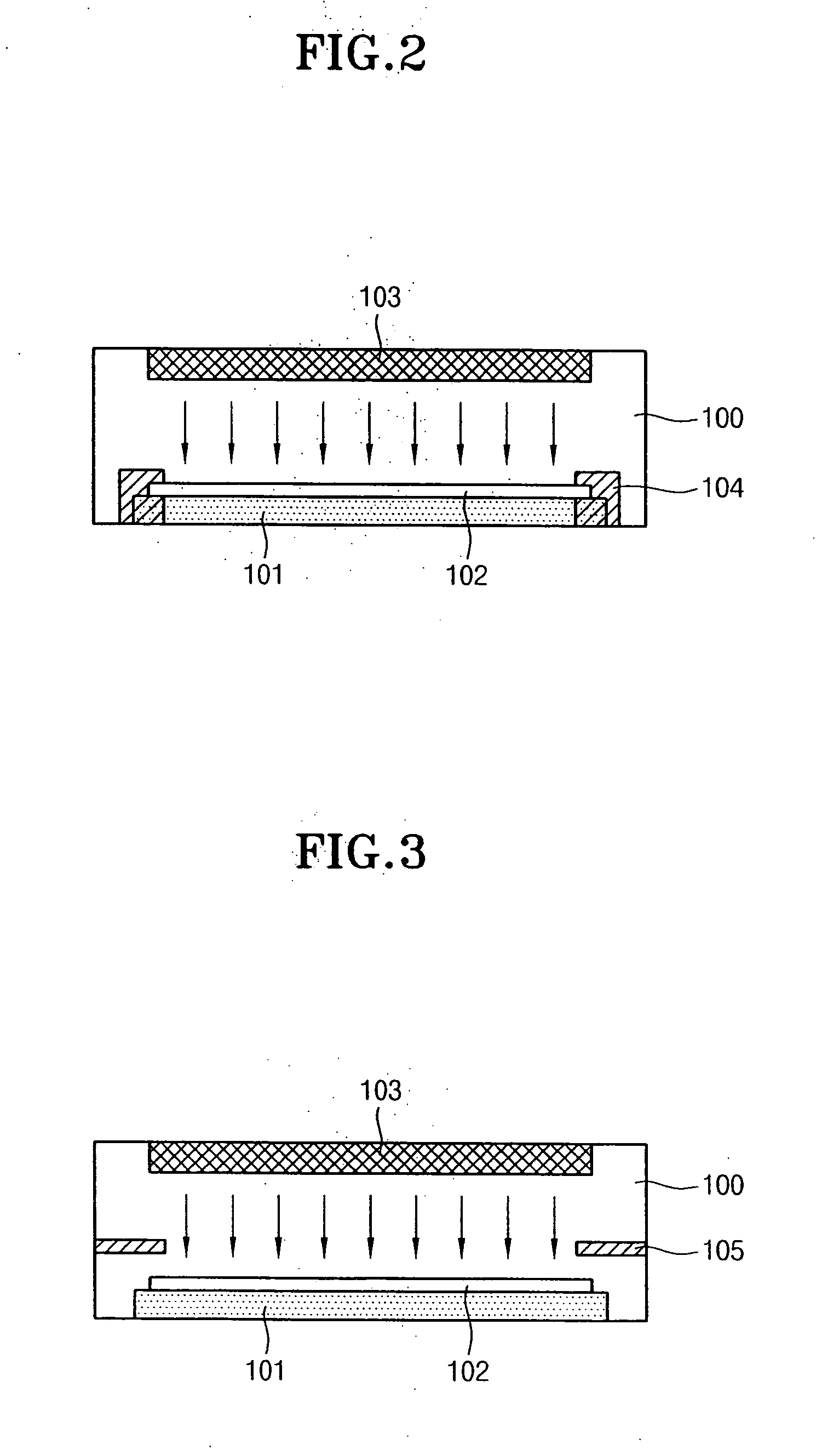

[0027] Referring to FIG. 2, in an apparatus for fabricating semiconductor devices, a processing chamber 100 used in an ion etching process is housed with a wafer chuck 101 for holding a wafer 102, a gas injection head 103 for injecting gas toward the wafer 102, and a clamp 104 for grasping the wafer 102 and preventing an edge of the wafer from being etched.

[0028] The wafer 102 is subjected to deposition of various thin layers thereon, and then patterned in a predetermined pattern by a photolithography process and an etching process.

[0029] In the photolithography process, to restrict photoresist contamination and particle generation, the edge o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com