Silicon wafer support fixture with roughended surface

a technology of support fixture and silicon wafer, which is applied in the direction of crystal growth process, polycrystalline material growth, chemically reactive gas, etc., can solve the problems of reducing the yield of operable integrated circuit dies obtained from the wafer, thermal cvd tends to coat all surfaces exposed in the furnace, and significant problems with particle production, so as to achieve convenient formation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

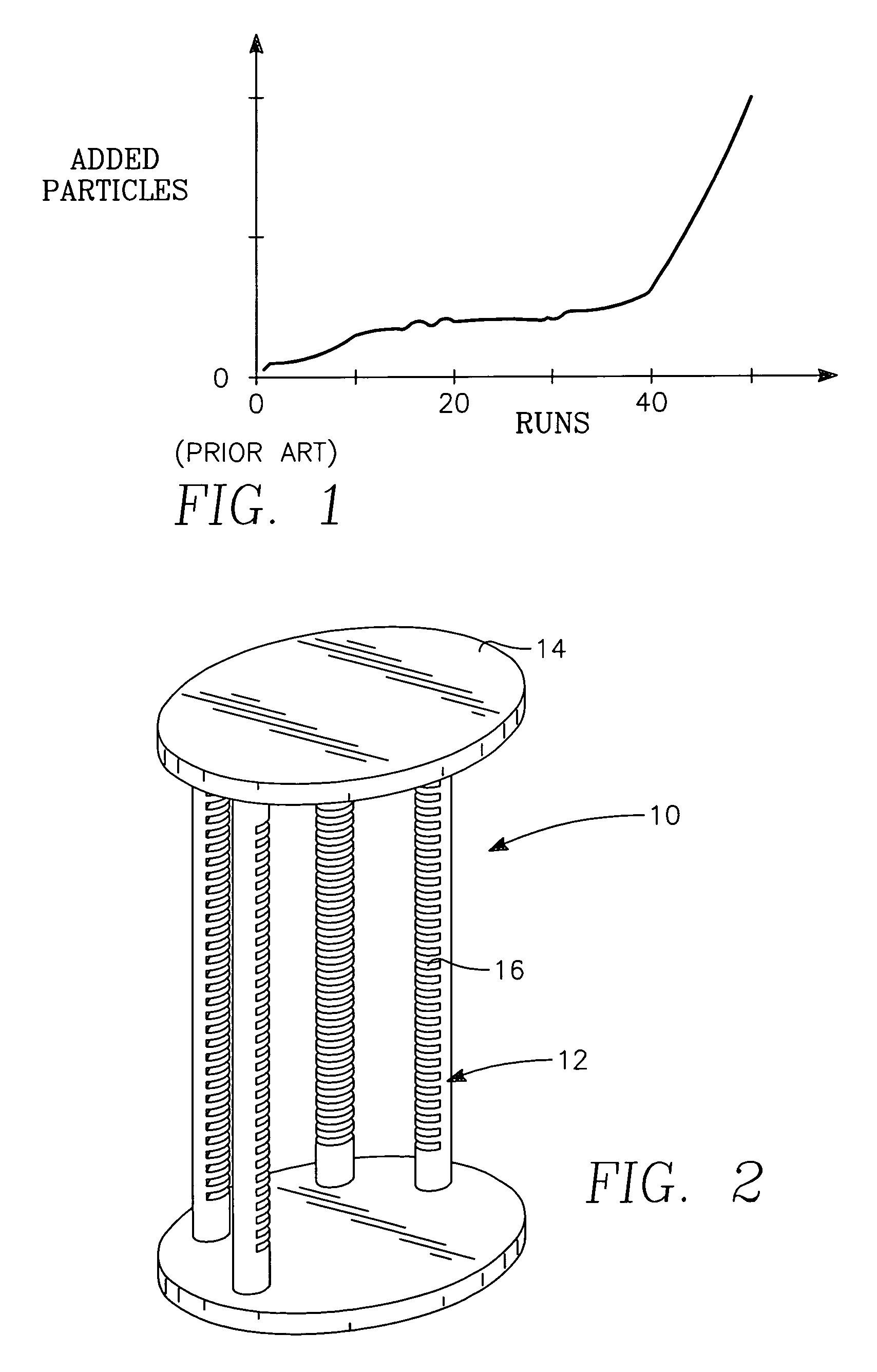

[0026] Silicon fixtures, particularly horizontally extending boats, have been frequently suggested and occasionally used in the past. However, their assembly has presented sufficient problems to prevent the widespread use of silicon towers. Many of these problems with silicon support fixtures have been addressed in a set of patents, U.S. Pat. Nos. 6,196,211, 6,205,993, and 6,225,594 to various of Zehavi, Davis, and Delaney. Boyle et al. in U.S. patent application, Ser. No. 09 / 608,291, filed Jun. 30, 2000, now issued as U.S. Pat. No. 6,455,395, and incorporated herein by reference in its entirety, disclose in detail a method of fabricating one embodiment of such a silicon tower 10, illustrated in FIG. 2. The tower 10 includes multiple silicon legs 12 joined at opposed ends to silicon bases 14. Teeth 16 are cut into the legs 12 to support the wafers.

[0027] It is preferred that at least the legs 12 are composed of virgin polysilicon (virgin poly) formed from the chemical vapor deposit...

PUM

| Property | Measurement | Unit |

|---|---|---|

| temperatures | aaaaa | aaaaa |

| roughness | aaaaa | aaaaa |

| roughness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com