Isolation structures for semiconductor integrated circuit substrates and methods of forming the same

a technology of integrated circuit substrate and isolation structure, which is applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of reducing the value of the isolation structure of the trench, reducing the processing efficiency of the trench, so as to achieve high flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

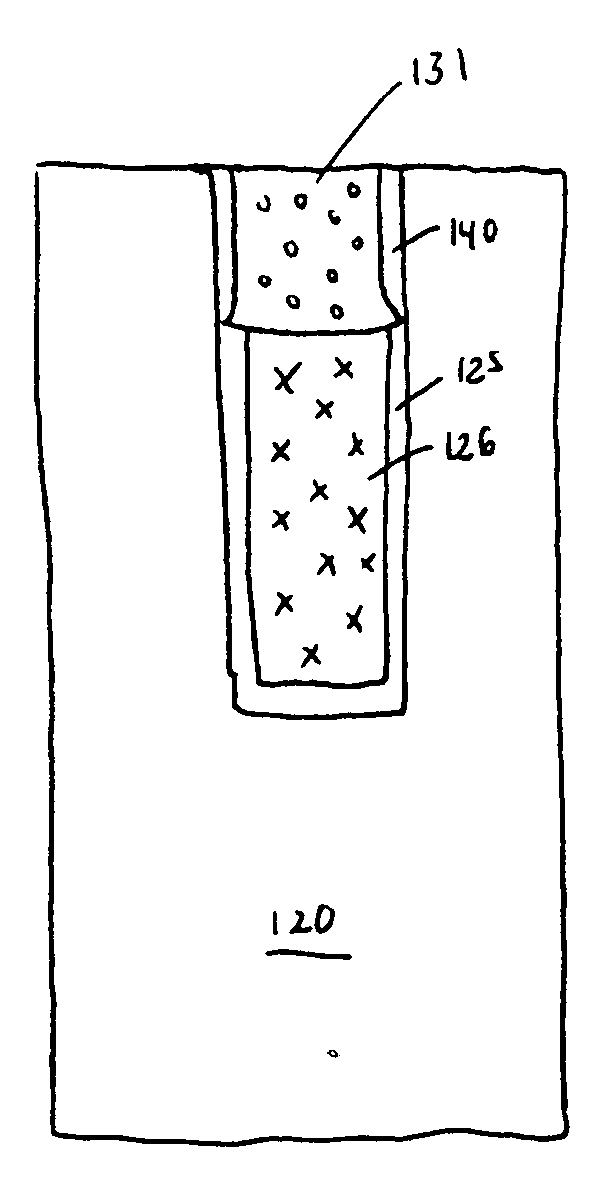

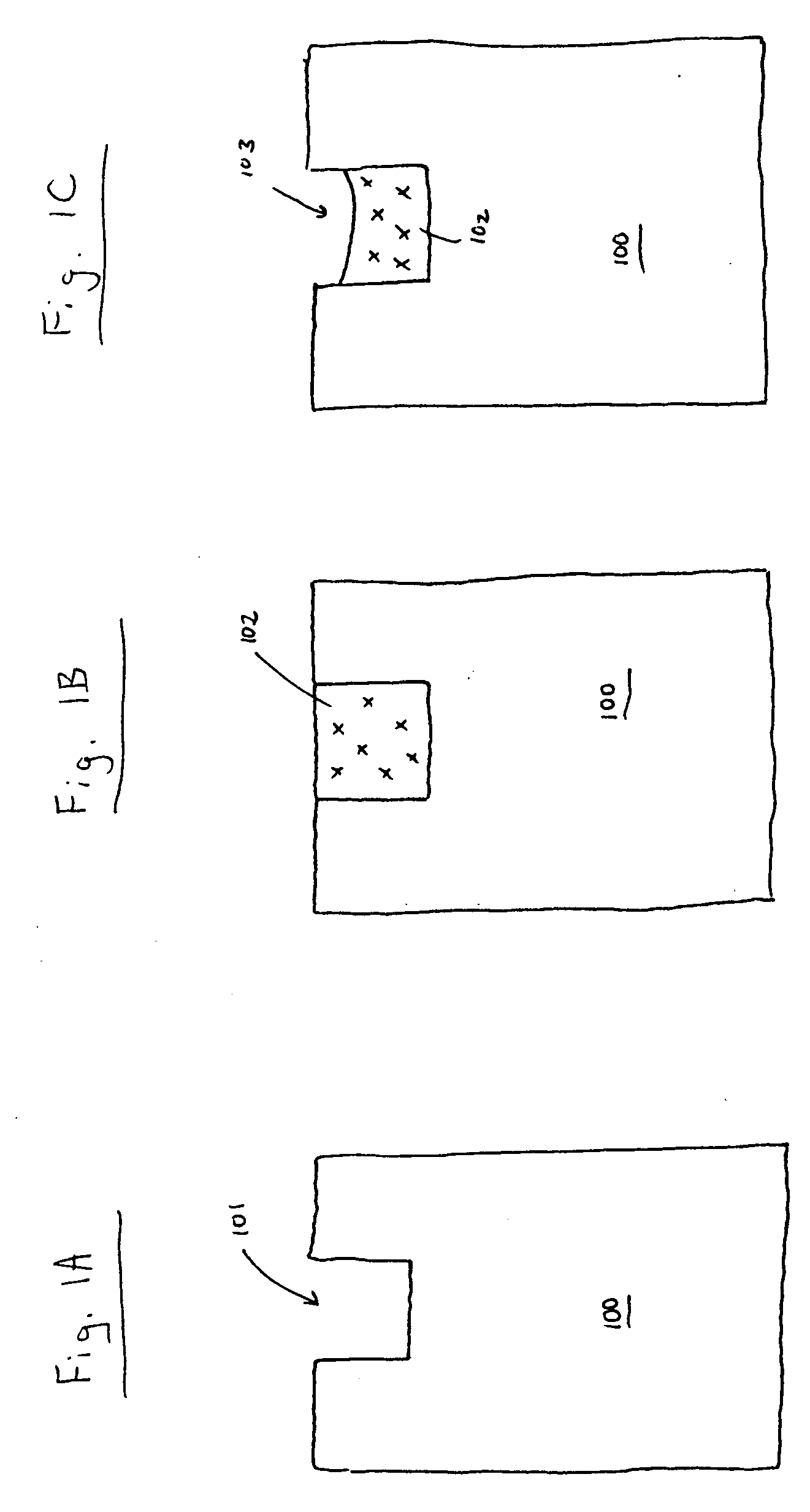

[0027]FIGS. 2A-2F illustrate a process for fabricating a trench isolation structure that avoids the formation of a gap or recess at the top of the trench, as shown in FIG. 1C. As shown in FIG. 2A, an oxide or “hard mask” layer 121 is formed on the top surface of a semiconductor substrate 120, and a photoresist layer 122 is deposited on top of hard mask layer 121. The term “hard mask” is used herein to refer to a thermally grown or deposited dielectric layer used as a mask during the etching of a trench in semiconductor substrate 120. The “hard mask” is distinguished from the organic photoresist layer 122, for example, which is mechanically softer and therefore subject to erosion during the trench etch process. An opening is formed in photoresist layer 122 by a normal photolithographic process, and an opening 123 is etched in hard mask layer 121 through the opening in photoresist layer 122.

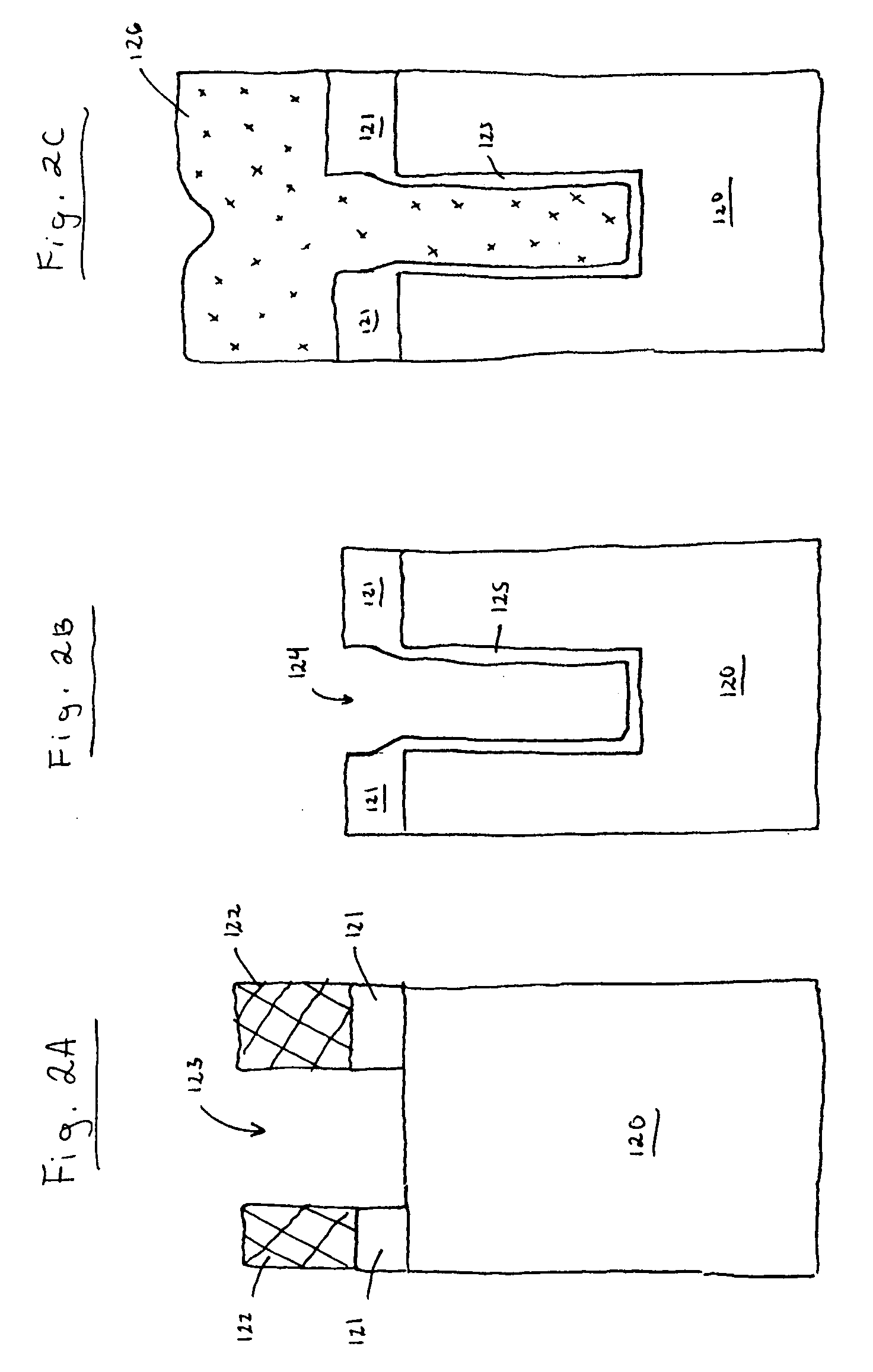

[0028] As shown in FIG. 2B, substrate 120 is etched through the opening 123 to form a trench 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More