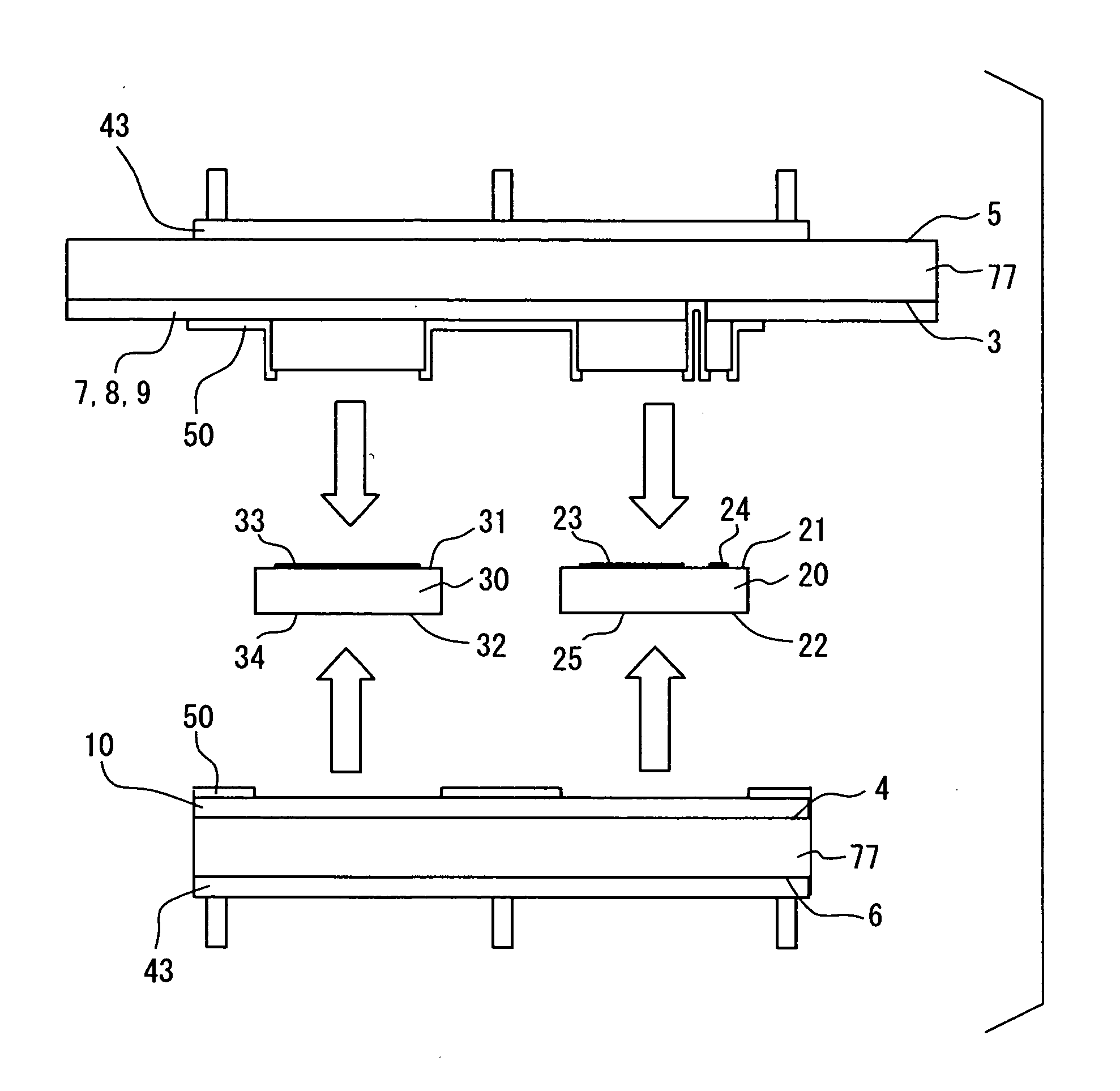

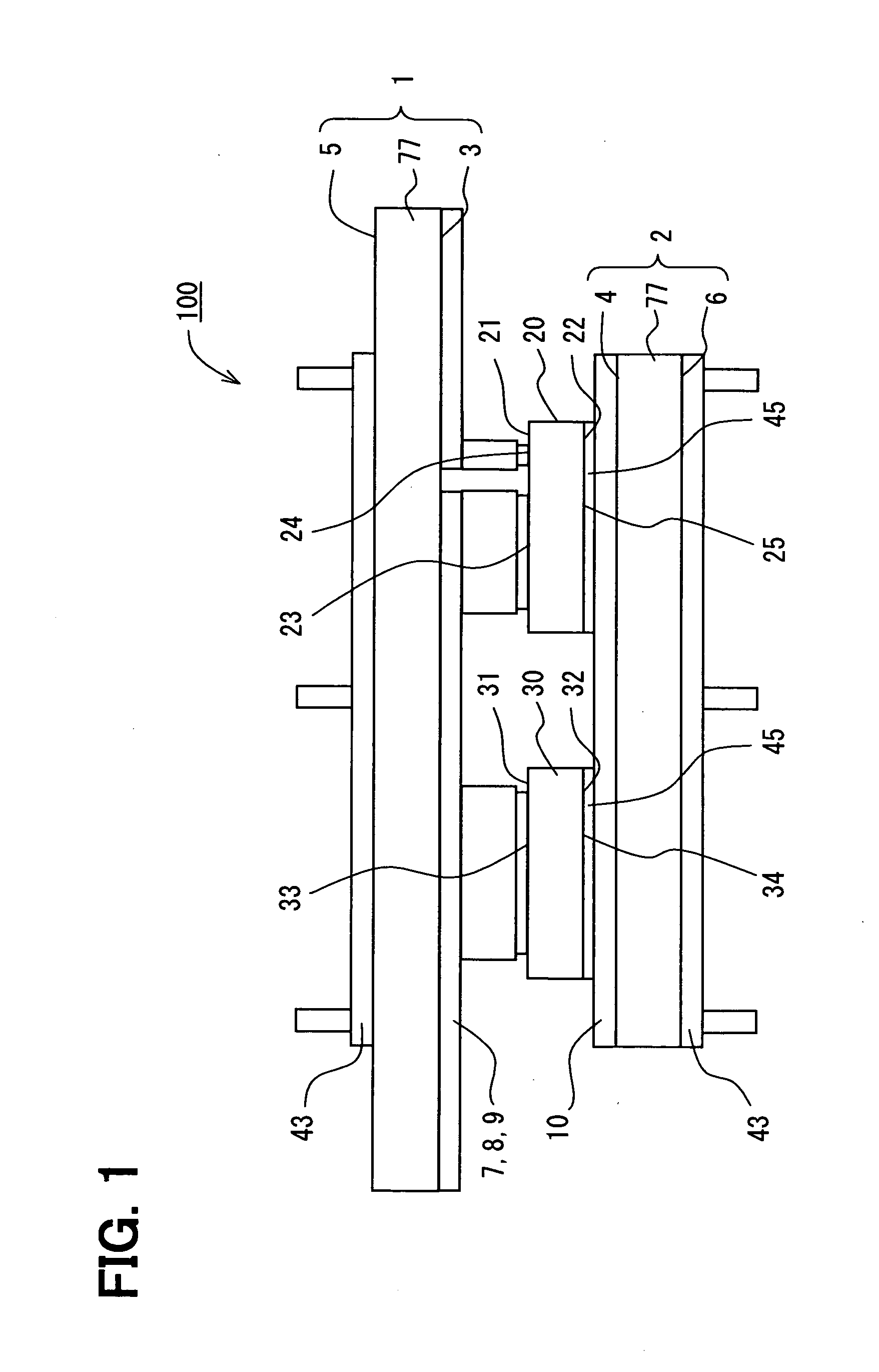

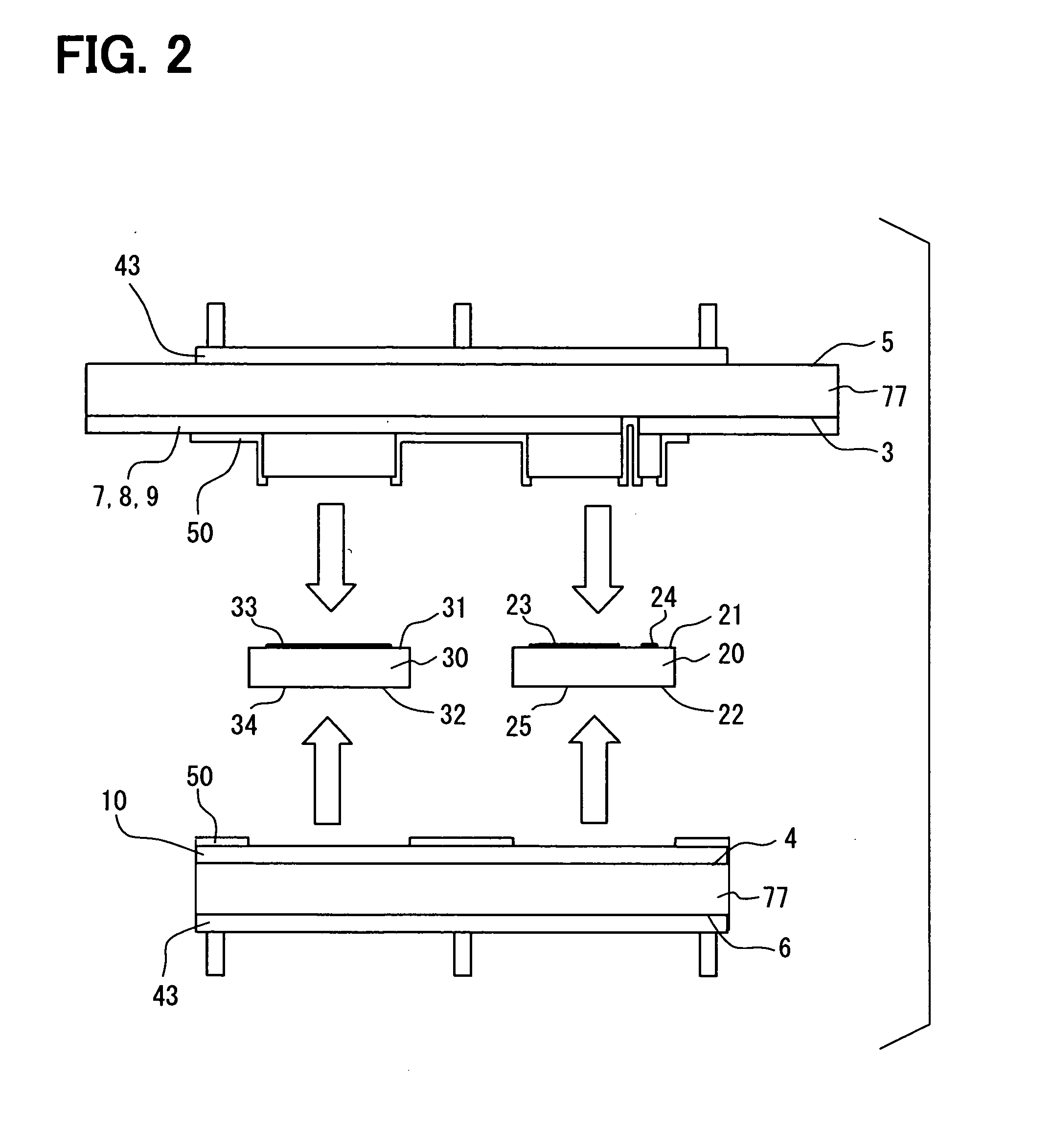

Power electronic package having two substrates with multiple semiconductor chips and electronic components

a technology of power electronic package and electronic components, which is applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problem of reducing the heat resistance of the power electronic package, and achieve the effect of improving reliability and heat radiation performan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0094]As shown in FIG. 31, each outer surface of the two high thermal conductive insulating non-planar substrates 1, 2 has not been etched for the improved integration with the heat exchanger 80. This example embodiment provide a freedom to use a integrated as well as a non integrated heat exchanger 80 for cooling the both side of the sandwich structure. The flat outer surface of the two high thermal conductive insulating non-planar substrates 1, 2 is suitable for using closed type micro-channel heat exchanger 80 unit using a thermal component in between to improve the heat radiation performance. However, this leads to a larger thermal resistance of the power electronic package 100. However, this configuration relaxes the total stress on the sandwich structure due to lack of direct bonding of the heat exchanger 80 unit. This structure can also be mounted on the air-cooled heat exchanger 80 units. The rest of the construction is the same as that of the With this kind of construction...

fourth embodiment

[0100]As shown in FIG. 37, each outer surface of the two high thermal conductive insulating non-planar substrates 1, 2 has not been etched for the improved integration with the heat exchanger 80. This embodiment provide a freedom to use a integrated as well as a non integrated heat exchanger 80 for cooling the both side of the sandwich structure. Each flat outer surface of the two high thermal conductive insulating non-planar substrates 1, 2 is suitable for using closed type micro-channel heat exchanger 41 unit using a thermal component in between to improve the heat radiation performance. However, this leads to a larger thermal resistance of the power electronic package 100. However, this configuration relaxes the total stress on the sandwich structure due to lack of direct bonding of the heat exchanger 80 unit. This structure can also be mounted on the air-cooled heat exchanger 80 units. The rest of the construction is the same as that of the With this kind of construction also, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More