Method for manufacturing a semiconductor device

a manufacturing method and semiconductor technology, applied in the field of semiconductor technology, can solve the problems of high manufacturing cost, poor heat dissipation, and large leakage of planar bulk silicon cmos structure devices, and achieve the effects of reducing manufacturing cost, poor suppression of sce effects, and large leakag

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

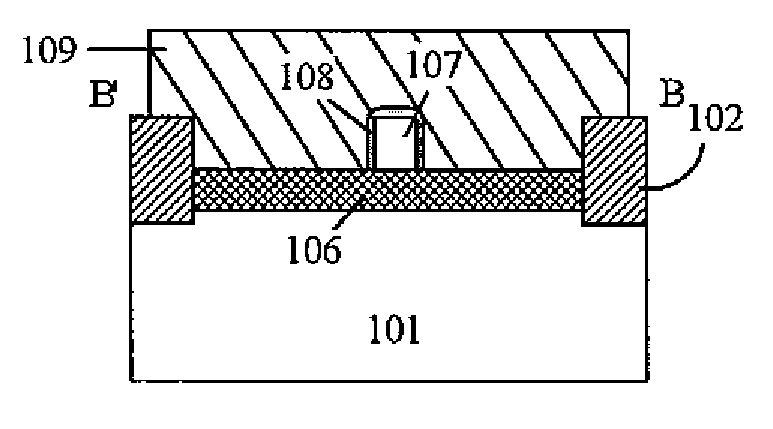

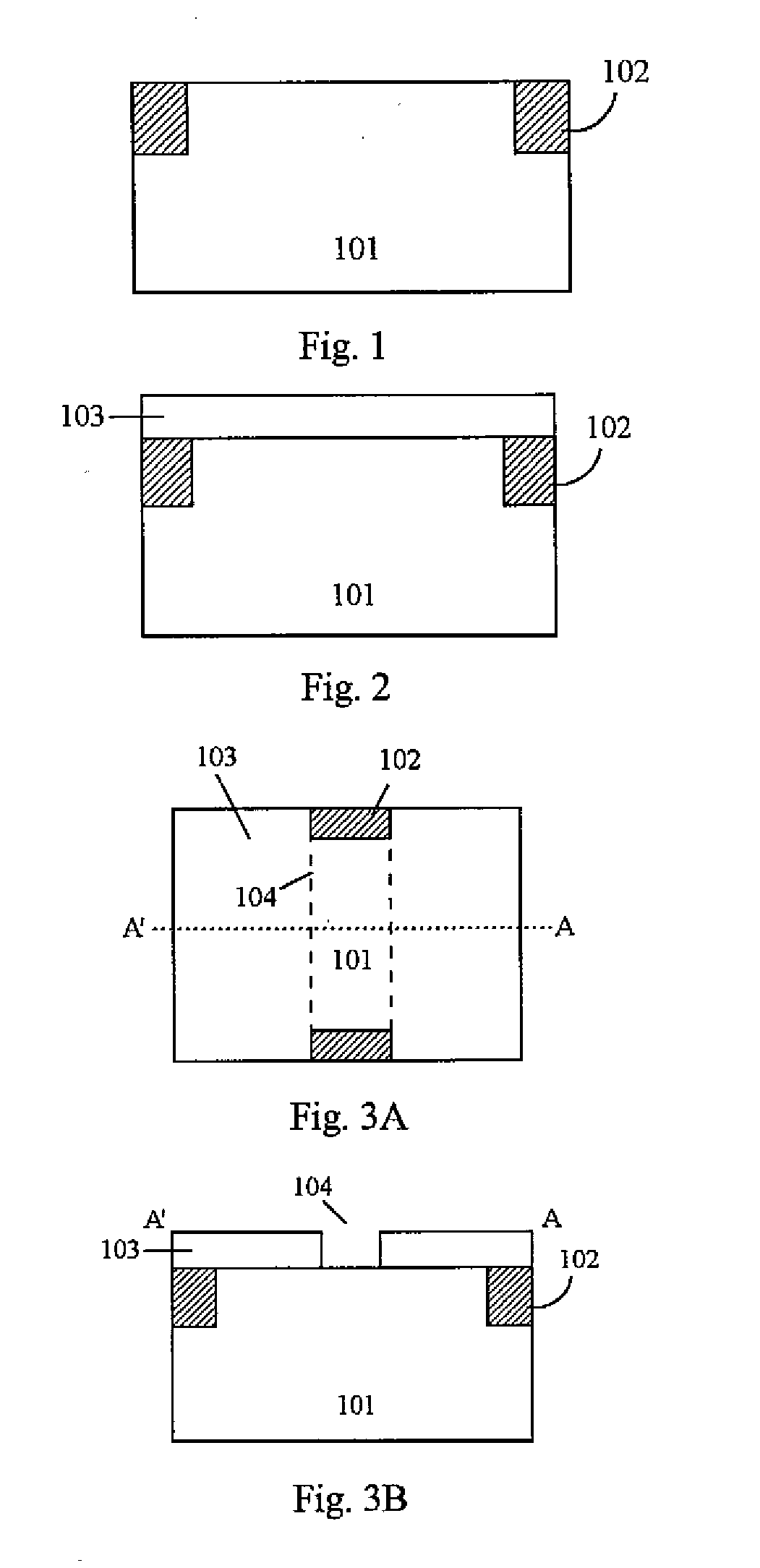

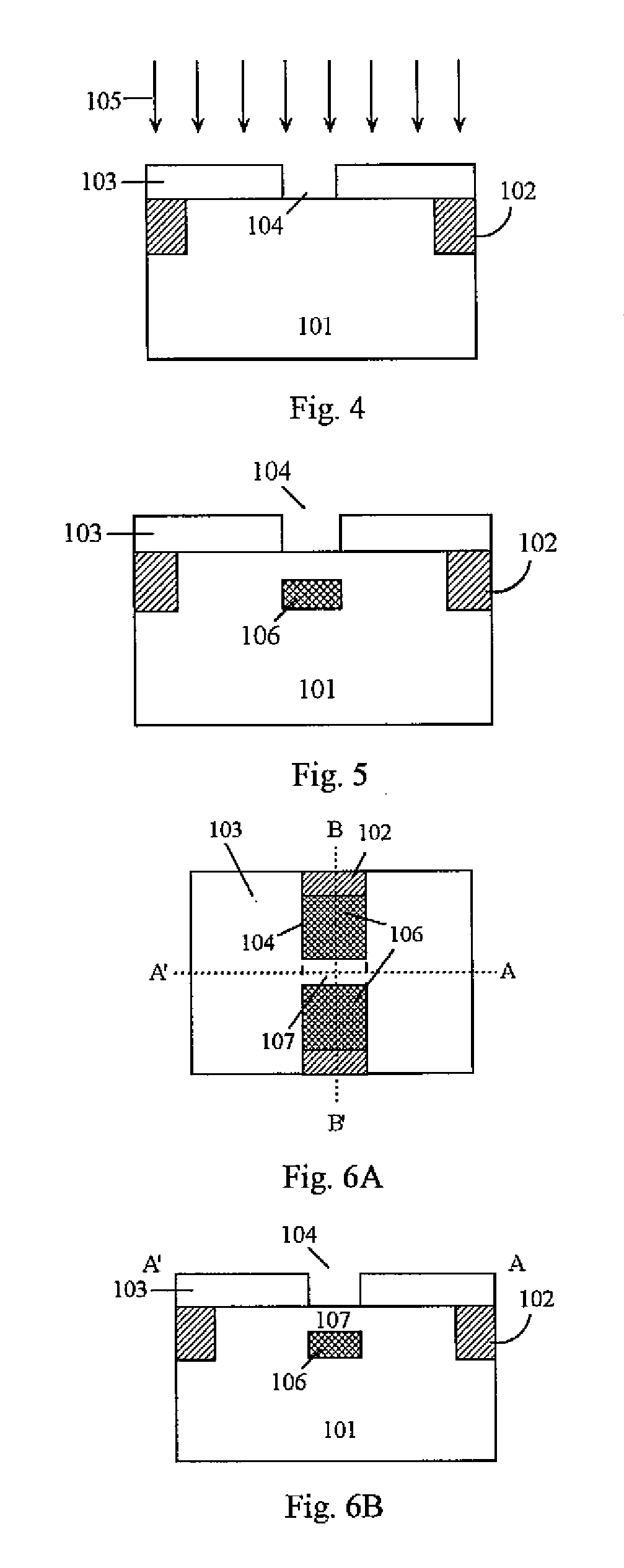

[0031]Hereinafter, the present invention will be described in accordance with a preferred embodiment shown in the attached drawings. However, it should be understood that the description is made for illustration only, rather than limitation to the scope of the present invention. Furthermore, in the following detailed description, the description of well-known structures and technologies are omitted to avoid obscuration of the present invention.

[0032]Schematic diagrams of the layer structure according to an embodiment of the present invention are shown in the attached drawings. These diagrams are not drawn to scale, but some details are exaggerated and other details are omitted for clarity. Shapes, relative sizes and position relationships of various areas and layers are only illustrative. Deviations may be introduced by manufacture tolerance or technical limitations in practice. Furthermore, areas / layers with different shapes, sizes, or relative positions may be designed by one skil...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More