Cooled electronics package with stacked power electronics components

a technology of power electronics and electronics components, applied in the field of electronics packages, can solve the problems of difficult packaging of power semiconductor chips very dense together, limited switching speed of power semiconductors, and parasitic inductance problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0008]It is an objective of the invention to provide an electronics package with densely packed power electronics components such as semiconductor chips, which is effectively cooled without degrading the electrical performance.

[0009]This objective is achieved by the subject-matter of the independent claims. Further exemplary embodiments are evident from the dependent claims and the following description.

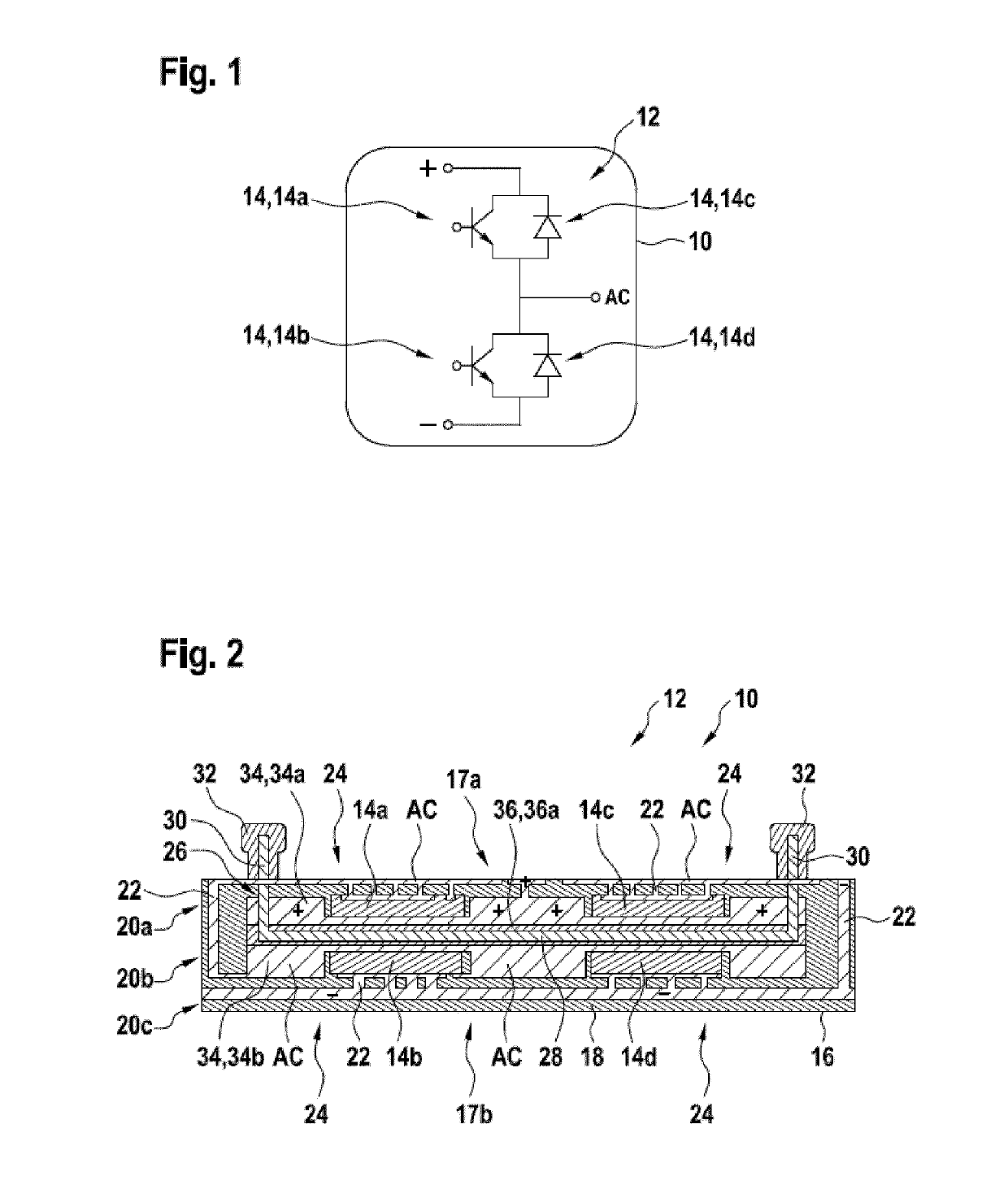

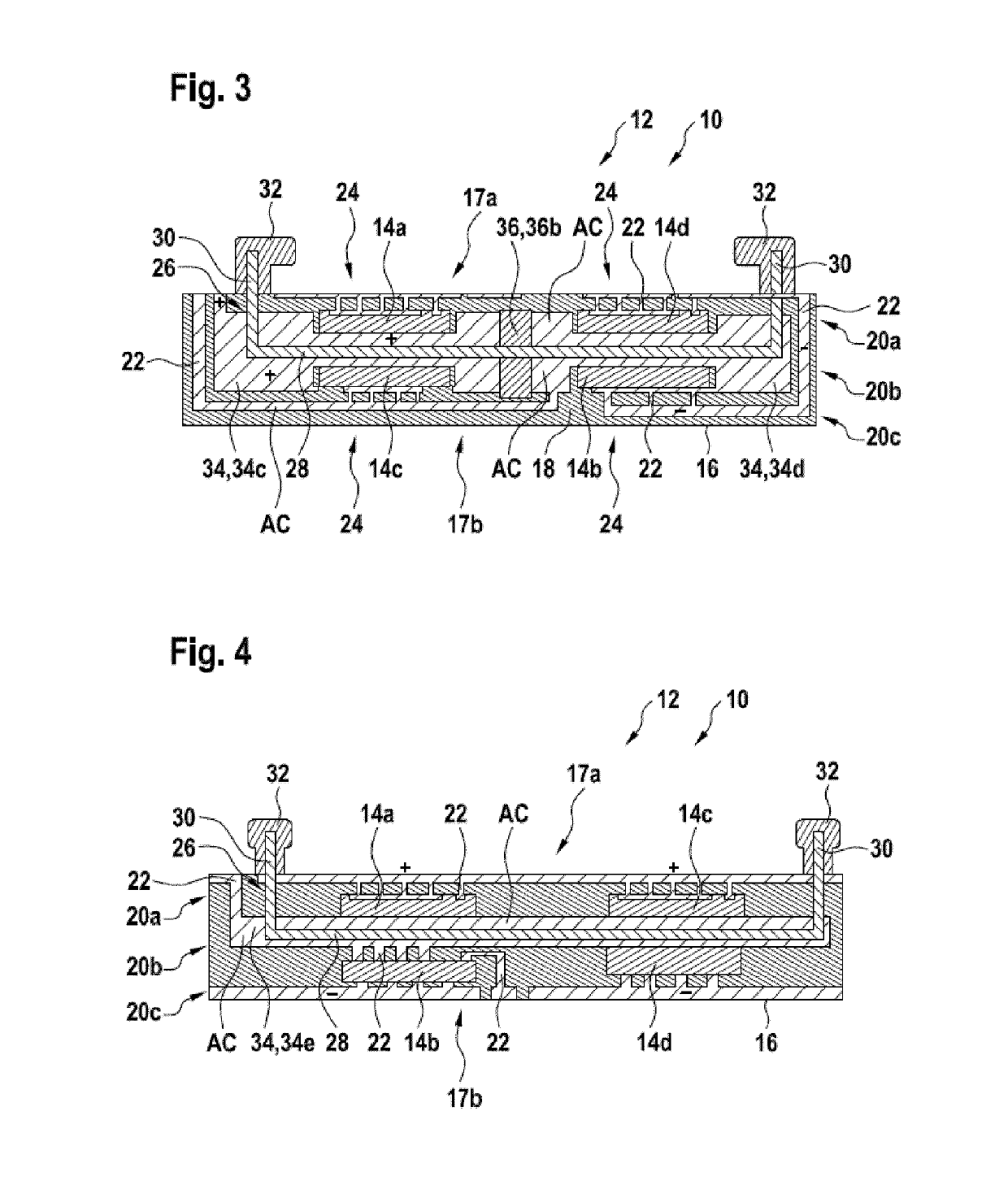

[0010]The invention relates to an electronics package, which may be an assembly comprising power electronics components, such as semiconductor chips, and electrical conductors which are mechanically and electrically interconnected. The electrical conductors may be provided in several layers, which are laminated together with isolation material, such as prepreg material. The power electronics components may be provided inside the electronics package and / or may be arranged in several layers. In such a way, the electronics package may be seen as a multi-layer circuit board.

[0011]The ele...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More