Method for making vertical double diffusion FET compatible conventional FET

A vertical double-diffusion and field effect tube technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem of decreased ability of control chip to monitor overheating of output chip, increased impact on circuit reliability, and increased packaging cost and other problems, to achieve the effect of solving reliability decline, realizing high-voltage and high-current control, and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

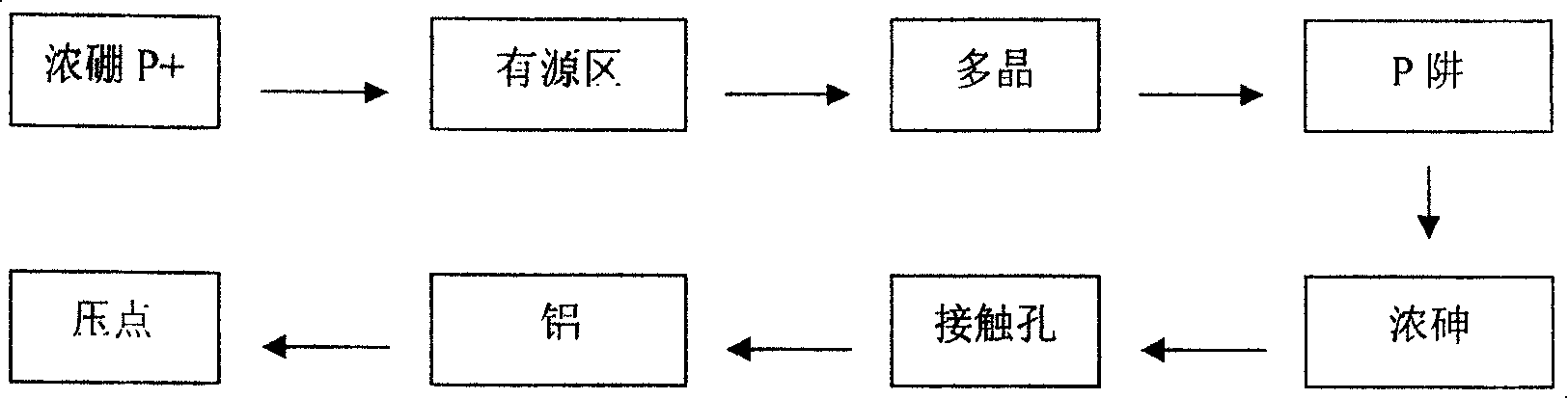

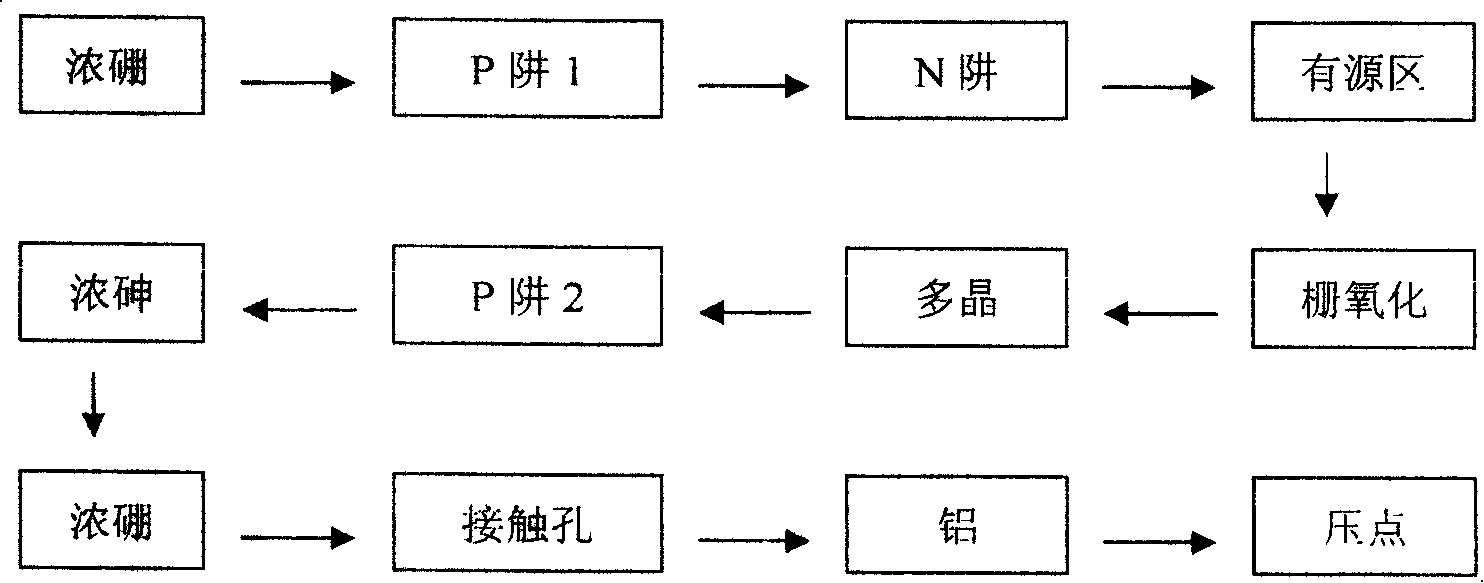

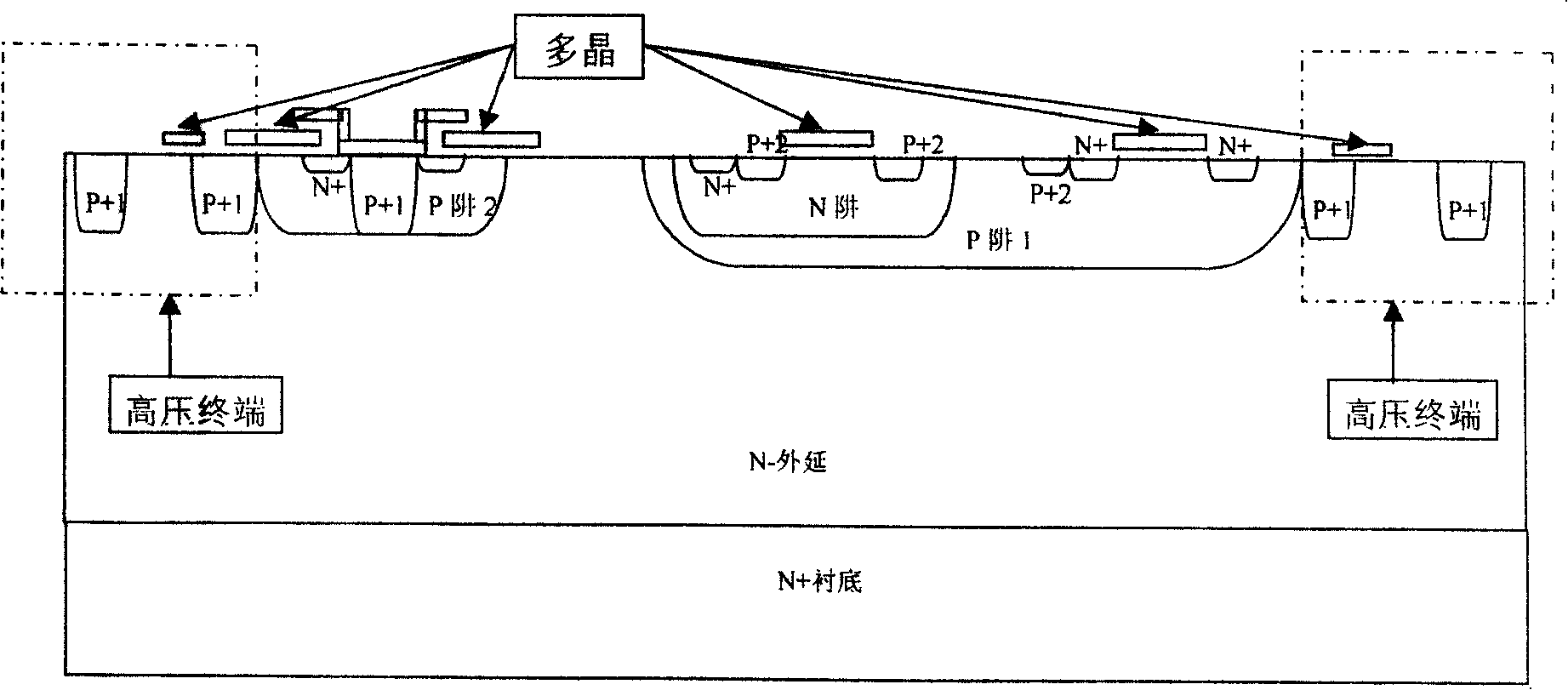

[0037] Under this platform, we have realized the integration of the control circuit and the output high voltage VDMOS on a chip area of 2000*2200μm. The specific implementation is as follows:

[0038] 1.) High-concentration P+ injection, pushing the junction depth: The concentration and junction depth here have a great impact on the voltage resistance of the entire die. The specific density and junction depth should be adjusted appropriately according to the corresponding layout design.

[0039] 2.) PWELL1 injection in low pressure area, pre-pushing the junction depth: here is just the pre-pushing the junction depth, don't push the junction depth too deep. Because there are many high-temperature processes behind, it will further deepen the junction.

[0040] 3.) Low-voltage area NWELL injection, pre-push junction depth: PWELL and NWELL for low-voltage CMOS are added before ACTIVE (active area). The junction depth of PWELL and NWELL here should not be pushed too deep, the advance...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More