Gate electrode and manufacturing method thereof

A manufacturing method and gate electrode technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems such as difficult to mature technology, opening is difficult to use in opening size, and cannot be mass-produced

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0164] On a semi-insulating GaAs substrate, a buffer layer, an InGaAs electron transport layer, an AlGaAs electron supply layer, and a GaAs low-resistance layer are sequentially stacked by MOCVD. In addition, after forming an active region by implanting oxygen, AuGe (20nm ) / Au(200nm) electrode to form an ohmic electrode.

[0165] Next, in the aforementioned active region in the gate electrode formation region, at both ends of the portion where the fine grid (gate electrode) is to be formed, the low-resistance layer portion in the region with a width of about 0.2 μm is excavated and removed to form a groove region. .

[0166] Secondly, if figure 2 As shown, on the substrate 1 on which the gate electrode is formed, a PMMA-based protective film (ZEP2000, manufactured by Japan Zeon (company name) Co., Ltd.) is coated with a thickness of 300 nm by spin coating, and heat-treated at 180° C. for 5 minutes. This forms the lowermost layer 2 . PMGI (manufactured by MCC Co., Ltd.) was...

Embodiment 2

[0175] Example 1 is the same as Example 1, except that the gate electrode forming surface driving step is performed after the gate electrode opening forming step and before the electron beam incident step and the gate electrode opening narrowing step.

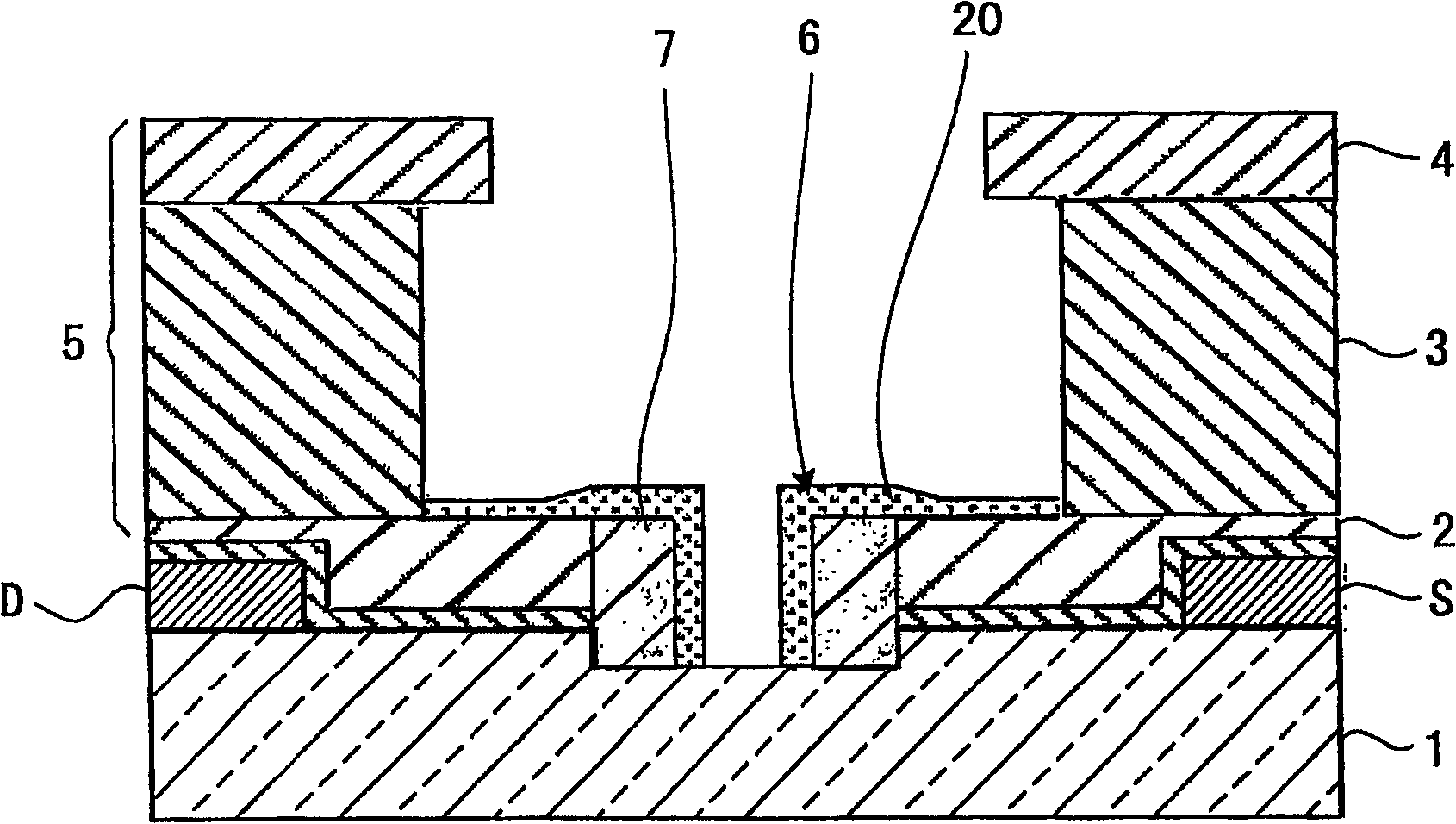

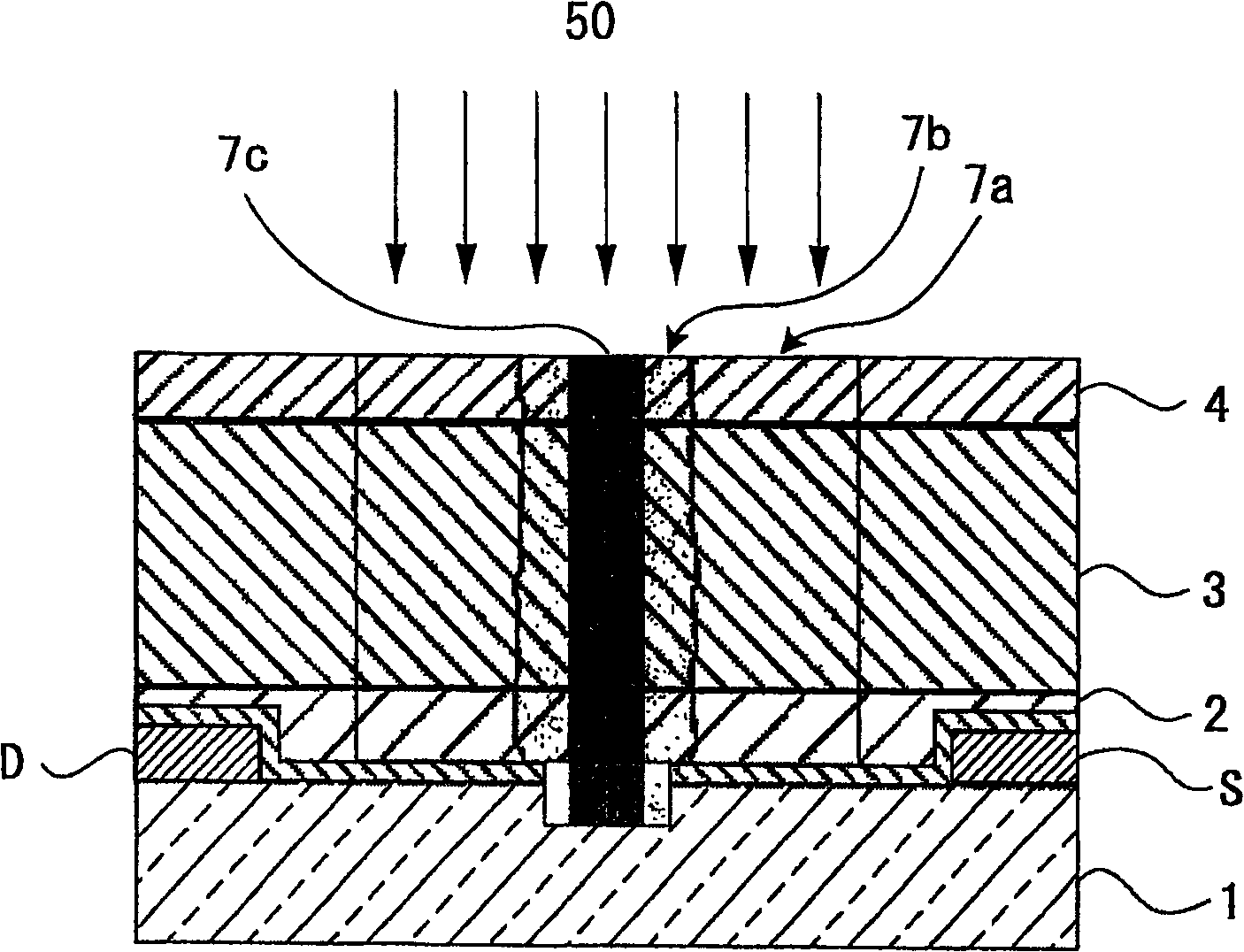

[0176] That is, specifically, as Figure 4A As shown, on the surface of the semiconductor substrate, source electrodes S and drain electrodes D are formed at regular intervals, and a SiN film is formed. Then, a multilayer protective layer 5 composed of the lowermost layer 2 , the intermediate layer 3 and the uppermost layer 4 is formed on the SiN film through the aforementioned multilayer protective layer forming step. Next, openings are formed in the uppermost layer 4 and the intermediate layer 3 in the laminated protective layer 5 through the aforementioned opening forming step. Then, the opening 10 for the gate electrode having an opening size of 0.2 μm was formed by the aforementioned opening forming step for the gate elec...

Embodiment 3

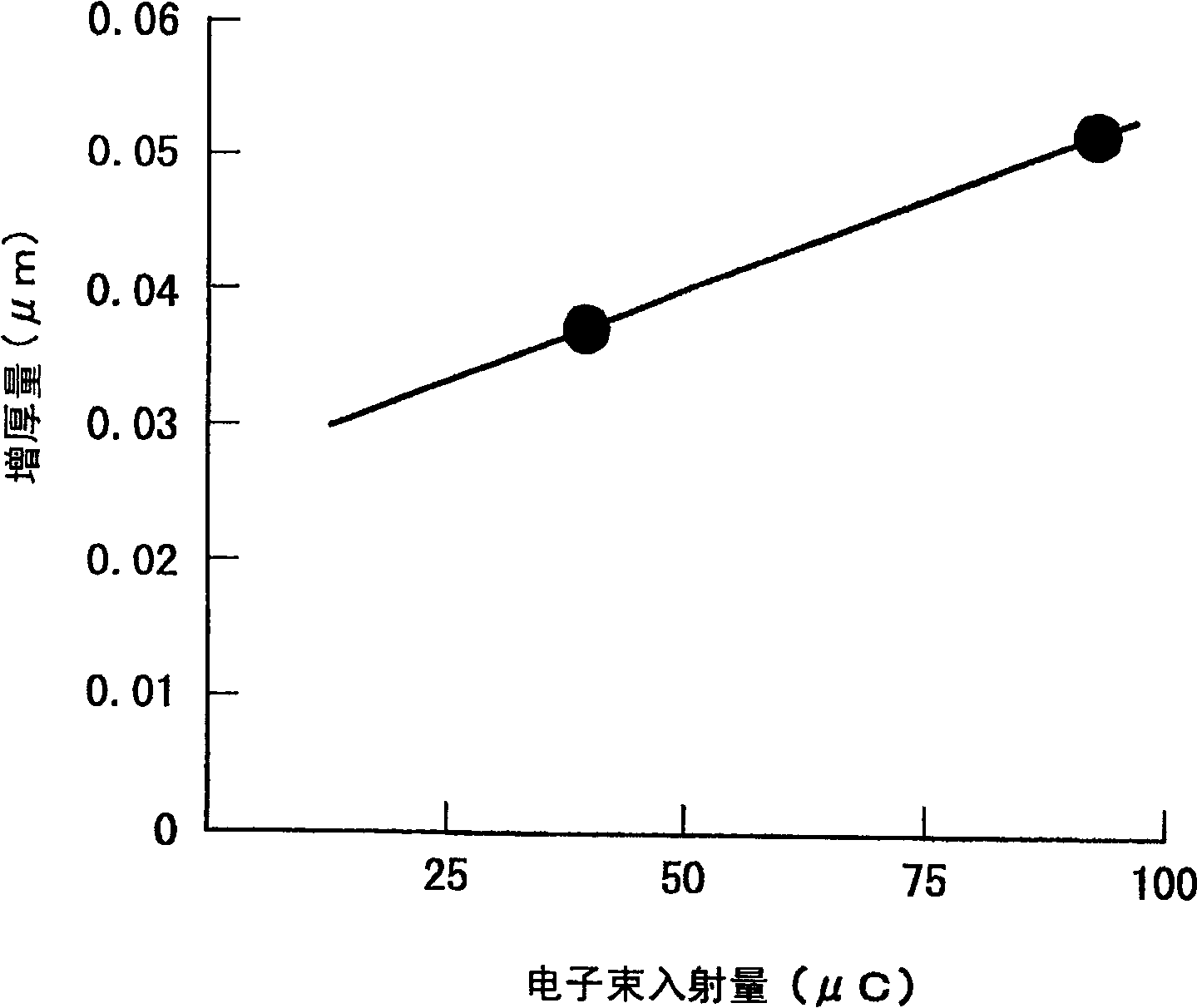

[0182]In Example 2, in the aforementioned electron beam incident step, since the opening size of the drain electrode D side of the gate electrode opening is selectively reduced, the incident is insufficient to develop Eth only on the drain electrode D side. Dose (60μC) (reference Figure 5A ~C).

[0183] results, such as Figure 5D As shown, for the gate electrode 30, the groove length on the D side of the drain electrode is 0.04 μm longer than the groove length on the S side of the source electrode, resulting in a field effect transistor with an offset gate.

[0184] Here, if the preferred mode of the present invention is annotated, it is as follows:

[0185] (Supplementary Note 1) A method for manufacturing a gate electrode, characterized by comprising: a step of forming a laminated protective film including an electron beam protective layer at least in the lowermost layer on a gate electrode forming surface; An opening forming step of forming an opening in a layer other ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com