A prodcution method for nano coulomb structure

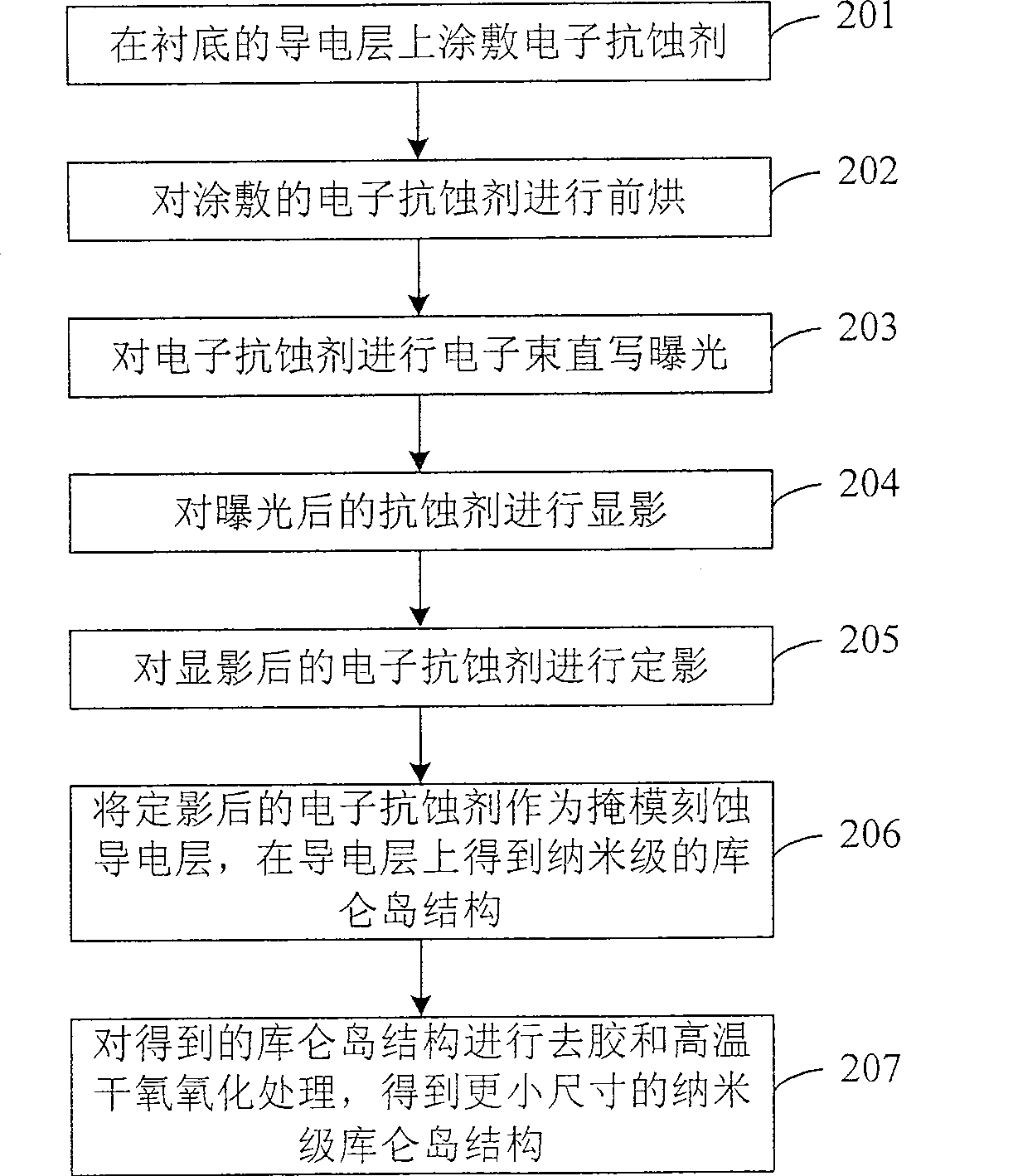

A nano-scale, tunnel junction technology is applied in the field of preparation of nano-scale Coulomb island structures, which can solve the problems of poor reliability, high preparation cost, complicated preparation process, etc., and achieve the effects of increasing working temperature, reducing preparation cost and improving preparation efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0092] This embodiment uses heavily doped SOI substrate, SAL601 chemically amplified negative electron resist, and ICP etching method, and further illustrates the detailed process and steps of the present invention in conjunction with the accompanying drawings.

[0093] Such as Figure 9 as shown, Figure 9 It is a schematic diagram of coating electronic resist SAL601 on SOI substrate. Coat SAL601 on a heavily doped n-type, (111) crystalline SOI substrate (consisting of three layers of silicon substrate 1, 160nm thick buried oxide layer 2 and 80nm thick top layer silicon 3 from bottom to top) Negative chemically amplified electronic resist 4 was applied at a rotation speed of 3000 rpm, and pre-baked at 120° C. for 3 minutes using a hot plate.

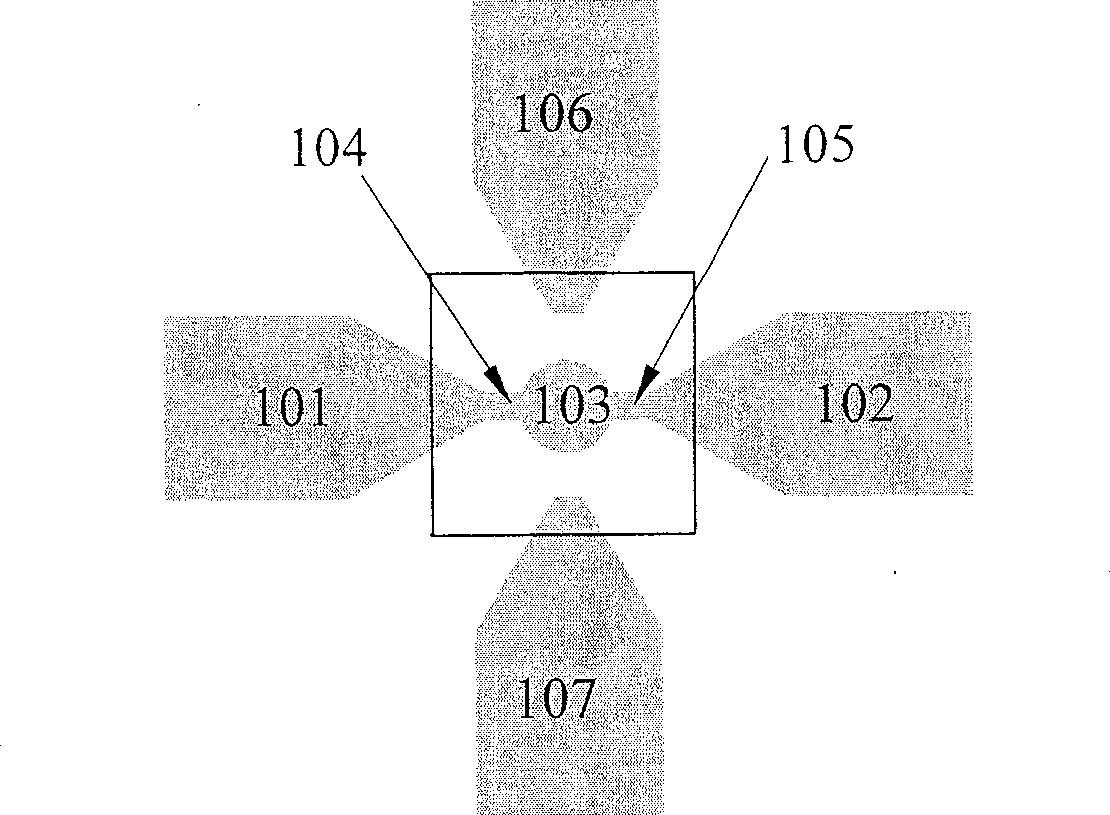

[0094] Such as Figure 10 as shown, Figure 10 It is a schematic diagram of forming a Coulomb island structure in electronic resist SAL601. Electron beam direct writing exposure, post-baking, and development are used to form Coulom...

Embodiment 2

[0098] In this embodiment, a heavily doped SOI substrate, ZEP520 positive electron resist, and ICP etching are used. In this embodiment, except for some conditions of EBL, other conditions are the same as those in Embodiment 1. The pre-baking conditions are baking at 160°C for 35 minutes in an oven; the exposure dose is 130 to 160μC / cm 2 ; no post-baking required; developed with amyl acetate for 4 minutes at room temperature and fixed with 4-methylpentanone 2 (MIBK) for 30 seconds at room temperature.

[0099] Figure 13 It is an actual SEM photo of the core part of the Coulomb island structure after ICP etching in the second embodiment of the present invention. The gray background in the figure is the buried oxide layer 2 of the SOI substrate; the white part corresponds to the top silicon layer 3 of the SOI substrate, and the middle point is the unoxidized Coulomb island 13, and the slightly larger figures on the left and right sides are the source 11 and drain 12, the par...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More