High-voltage MOSFET device

A high-voltage and device technology, applied in the direction of electric solid devices, semiconductor devices, electrical components, etc., can solve the problems that high-voltage transistors cannot be directly transferred and cannot be used to reduce the gate fringe electric field, etc., to achieve high breakdown voltage, production The effect of low cost and low process complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

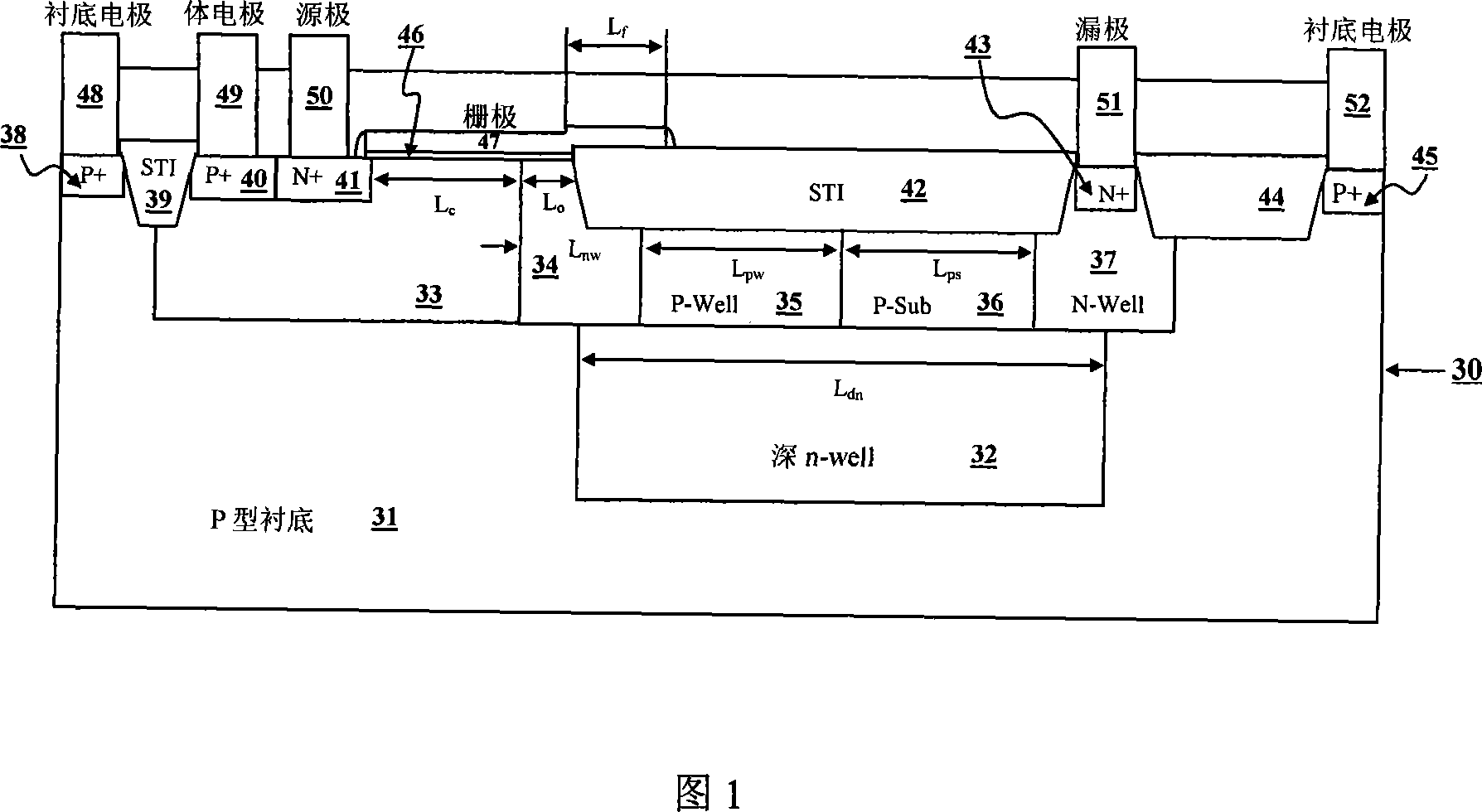

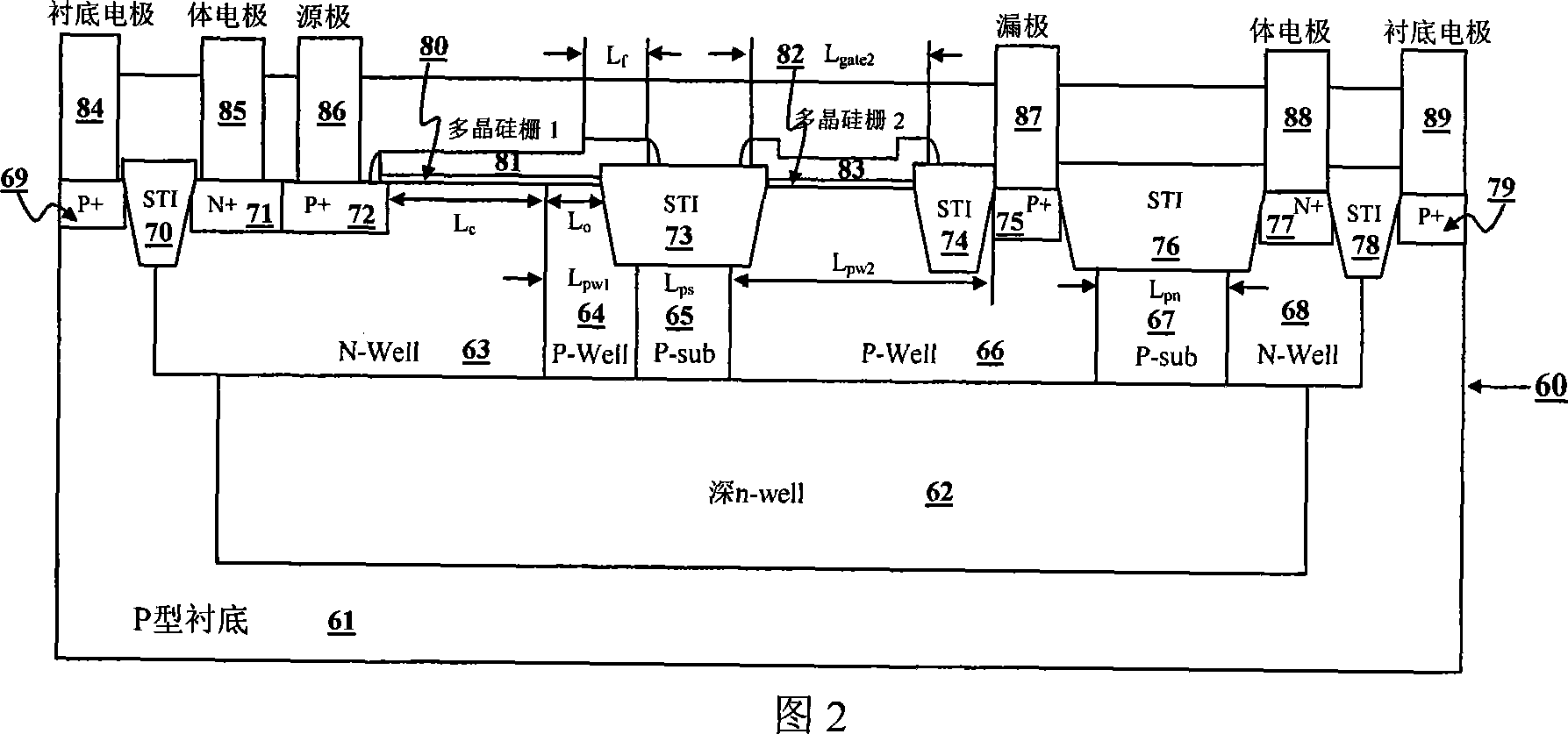

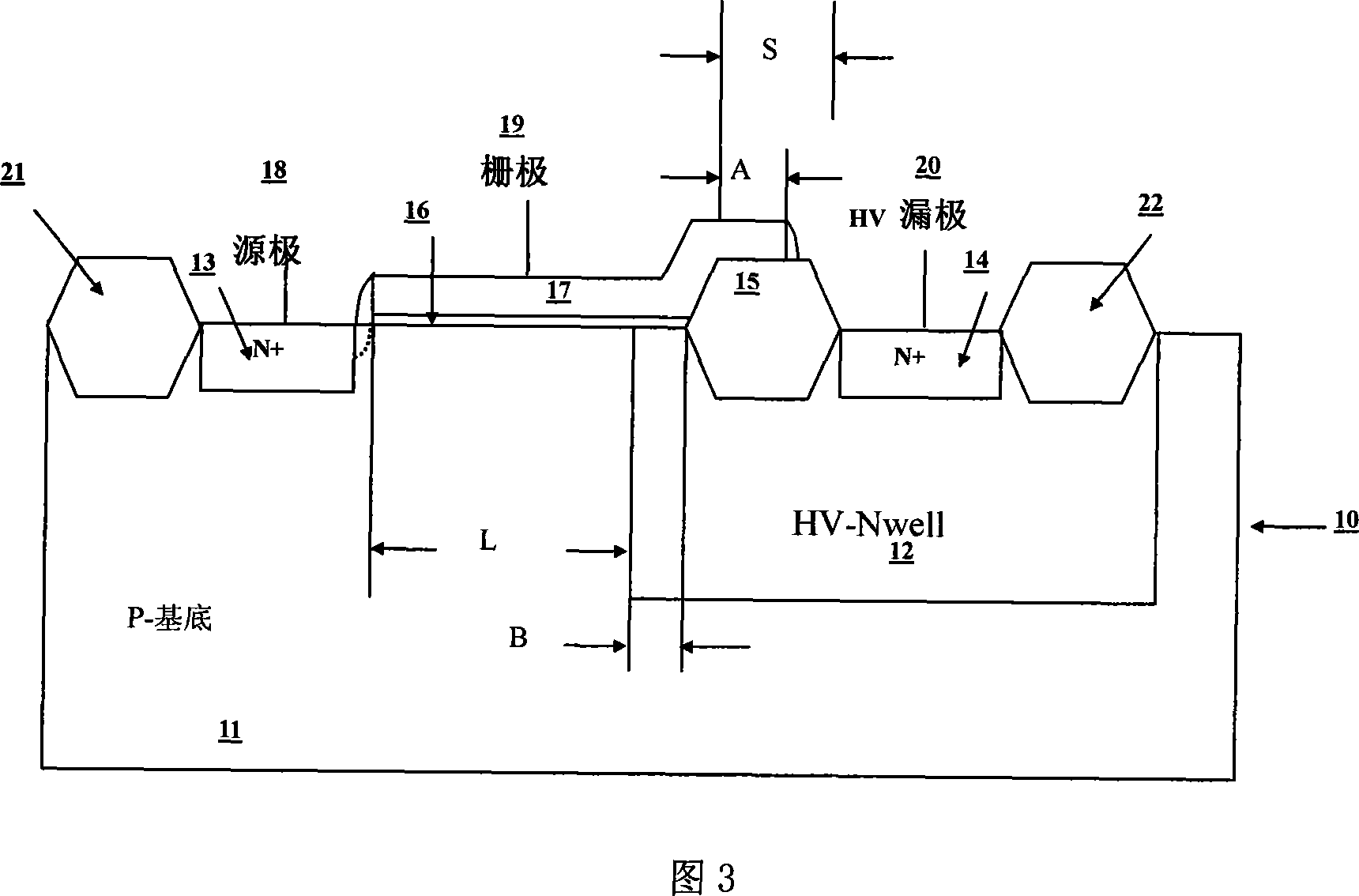

[0026]This new high-voltage NMOS structure is fully usable in standard submicron CMOS processes without changing any existing process steps. Body breakdown instead of silicon surface breakdown, breakdown resistance and reliability are all based on specially designed high-voltage device structures. The proposed HV NMOS structure uses a first n-well, a deep n-well, and a second n-well to create a buffer region between the channel and drain. The breakdown voltage is determined by the impurity concentrations of the first n-well, second p-well, deep n-well and p-type substrate. The surface impurity concentration of the first n-well is lower than that of the n-LDD of the low voltage device. The high breakdown voltage depends on the lateral extension of the first n-well under the gate, as shown by Lo. The second p-well is implanted close to the first n-well to achieve charge compensation, and the length of the compensation region depends on the process design criteria of the used p...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Length | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More