Single gate pole non-volatile internal storage and its operation method

A non-volatile, method-of-operation technology, applied in the field of non-volatile memory, which can solve the problem of reducing the current requirement of programming single gate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 5 example

[0135] In addition, the present invention also provides a fifth embodiment, which uses a negative voltage applied to the P-type well, so that the absolute voltage of the drain or gate becomes smaller (less than 5V) during programming and erasing, so as to achieve low voltage and low consumption The operating effect of the current.

[0136] FIG. 9 is a cross-sectional view of a single-gate non-volatile memory structure provided by a fifth embodiment of the present invention.

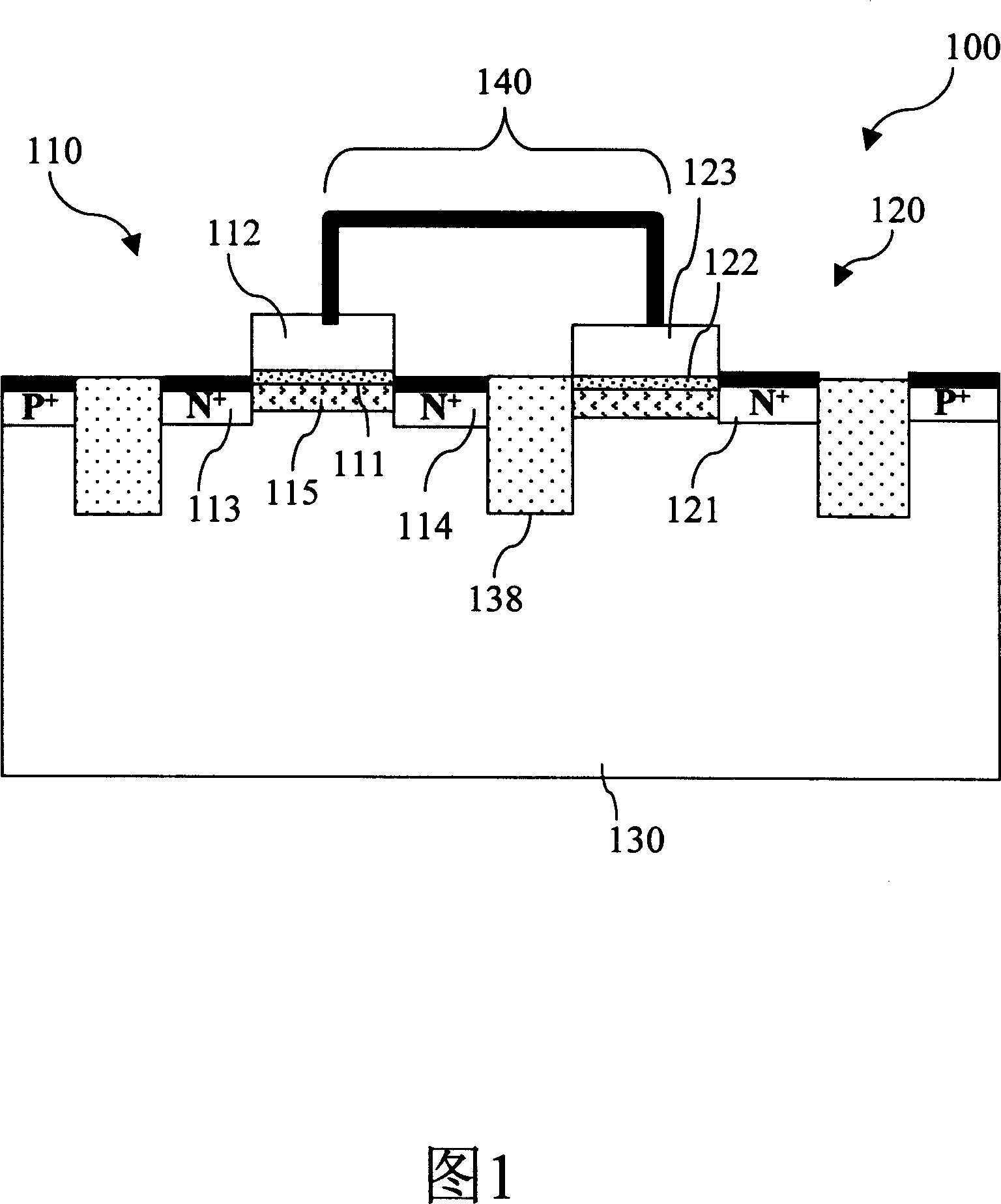

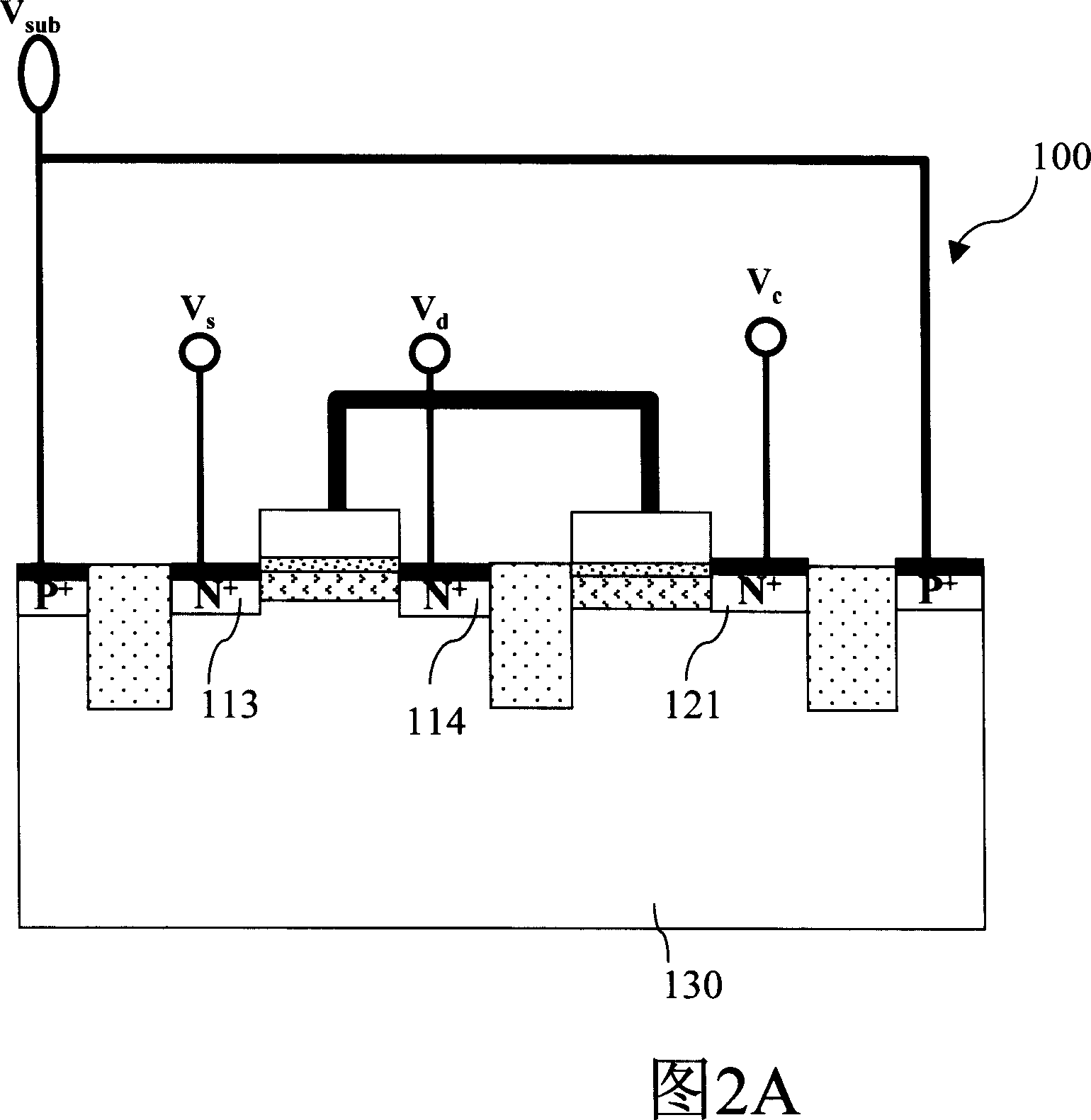

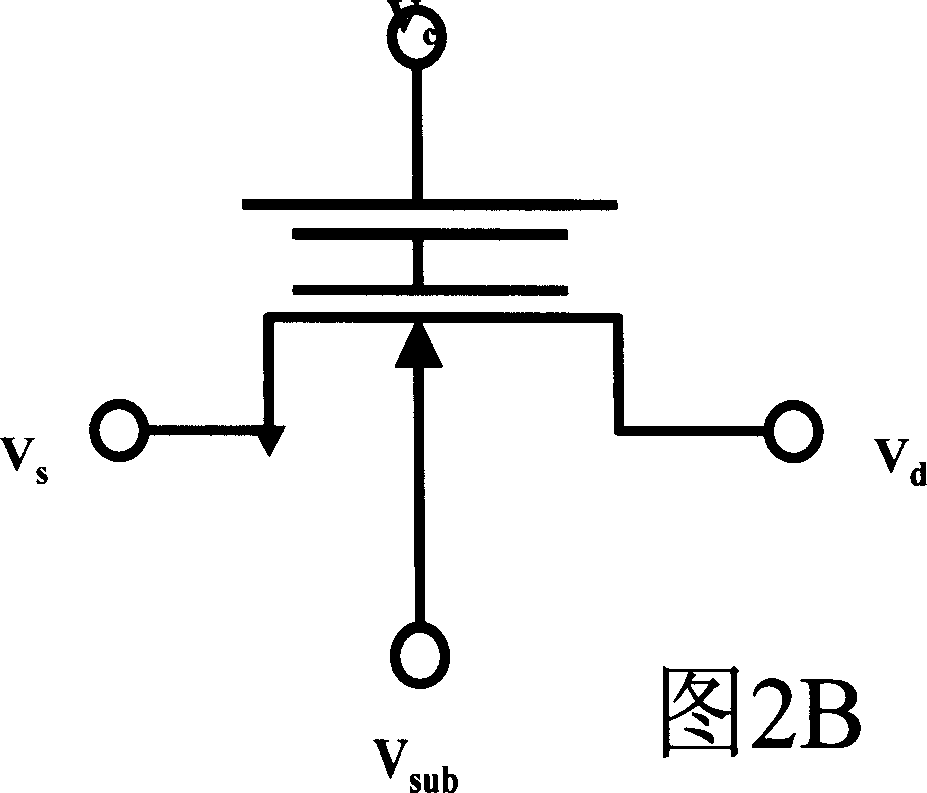

[0137] The single-gate non-volatile memory structure 500 includes an NMOS transistor 510 and an N-type capacitor structure 520 in a P-type well 517, and the P-type well 517 is disposed on an N-type semiconductor substrate 530; and the first conductive gate of the NMOS transistor 510 512 and the second conductive gate 523 on top of the N-type capacitor structure 520 are electrically connected and isolated by an isolation material 538 to form a single floating gate 540 structure.

[0138] For the single-ga...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More