Solid-state imaging device, imaging apparatus and camera

A technology for solid-state imaging devices and imaging devices, applied in semiconductor/solid-state device parts, electric solid-state devices, semiconductor devices, etc., can solve the problem of difficulty in reducing pixel size, disadvantageous high-speed driving, and increasing pixel circuit drive load pixel circuit Problems such as signal readout load

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 3 example

[0112] A third embodiment of the present invention will be described below with reference to the drawings. 8 is a block diagram illustrating one structural example of main units of an imaging device according to a third embodiment of the present invention.

[0113] The imaging device 2001 includes a pixel circuit 2010, a pixel array unit 2011, a horizontal scanning circuit (HSCN) 2012, an amplifier 2121, a vertical scanning circuit (VSCN) 2013, a signal processing circuit 2014, an analog-to-digital converter (A / D) 2015, a timing An adjustment unit 2016 , a timing generator (TG) 2017 , and a lens 2018 .

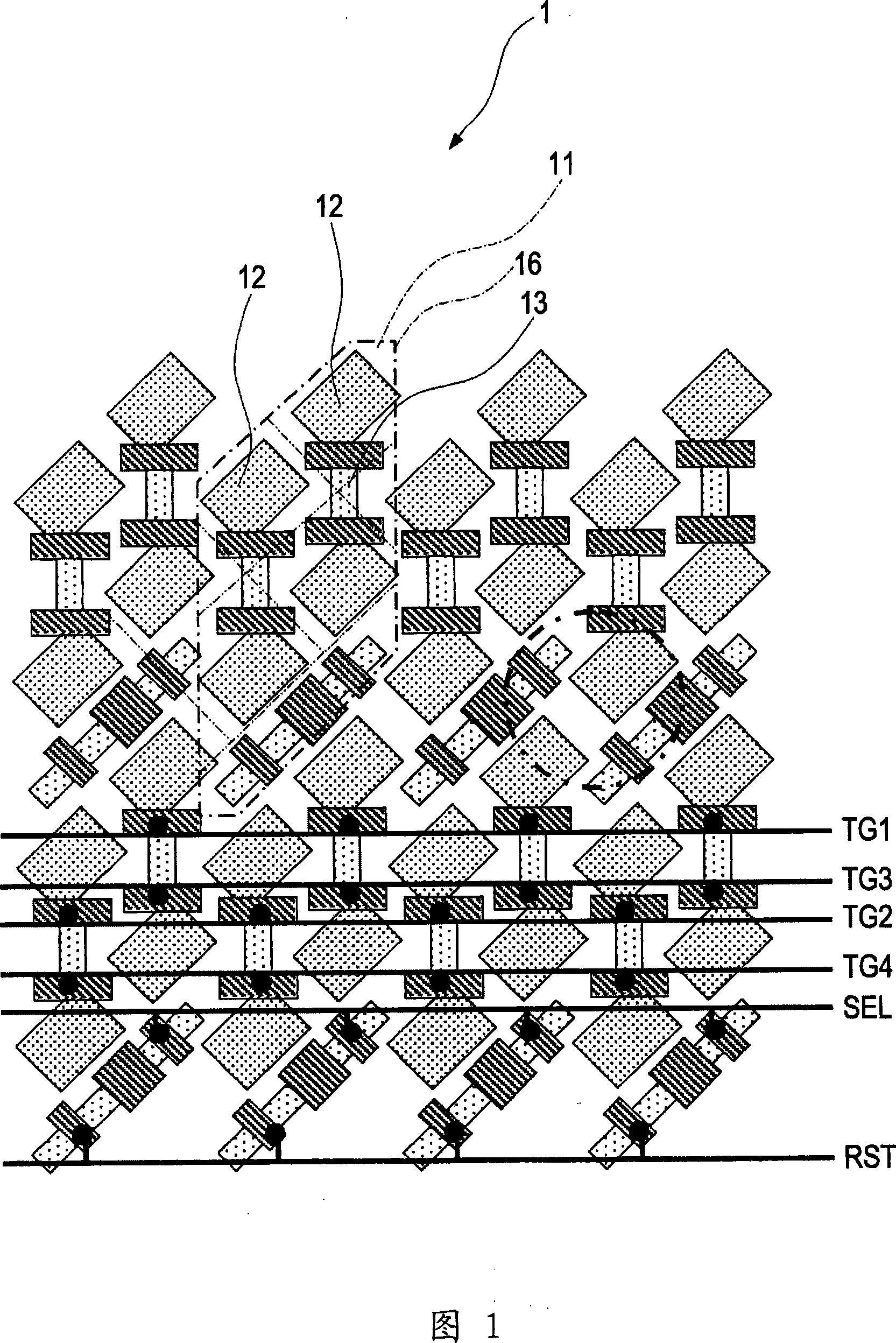

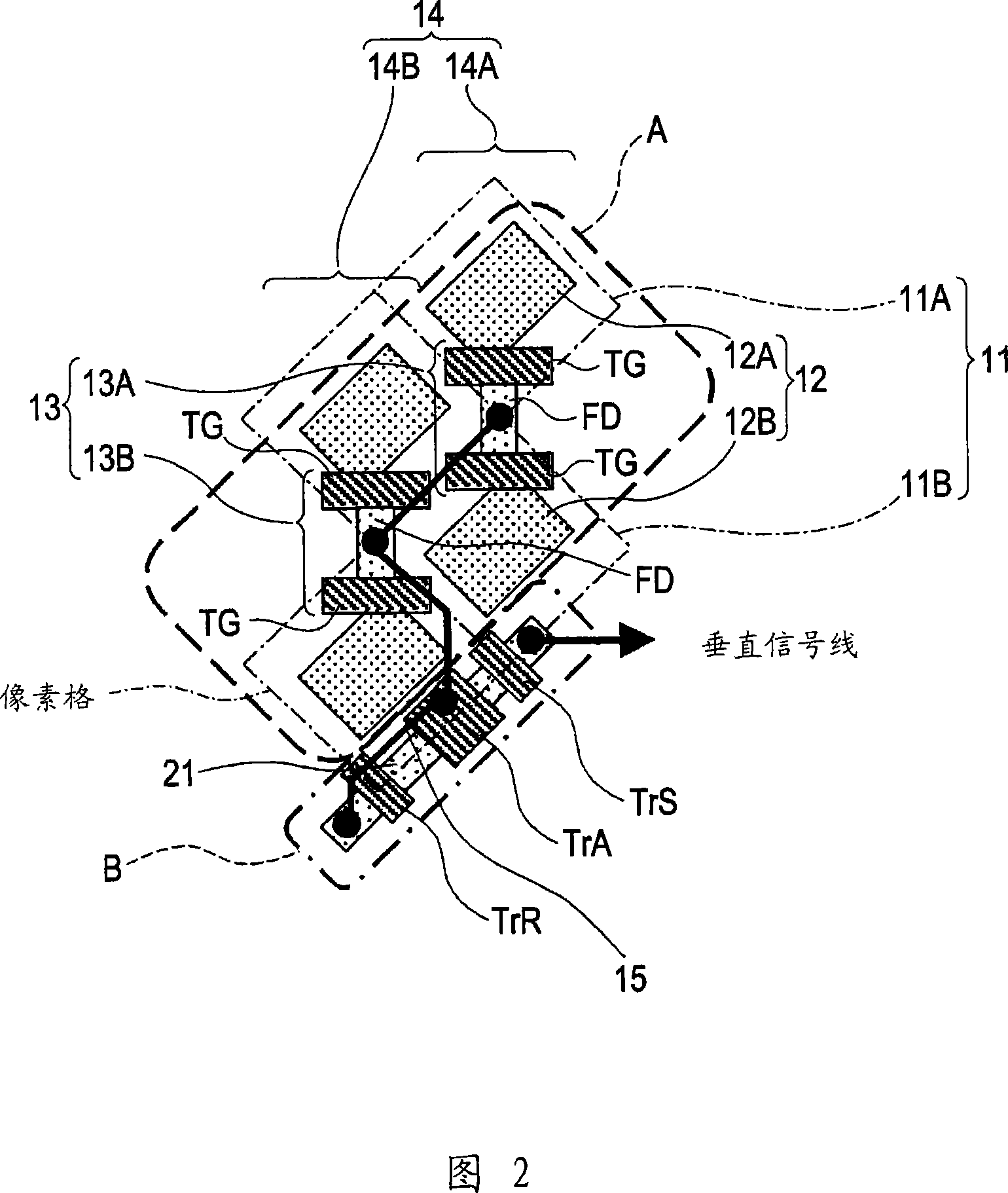

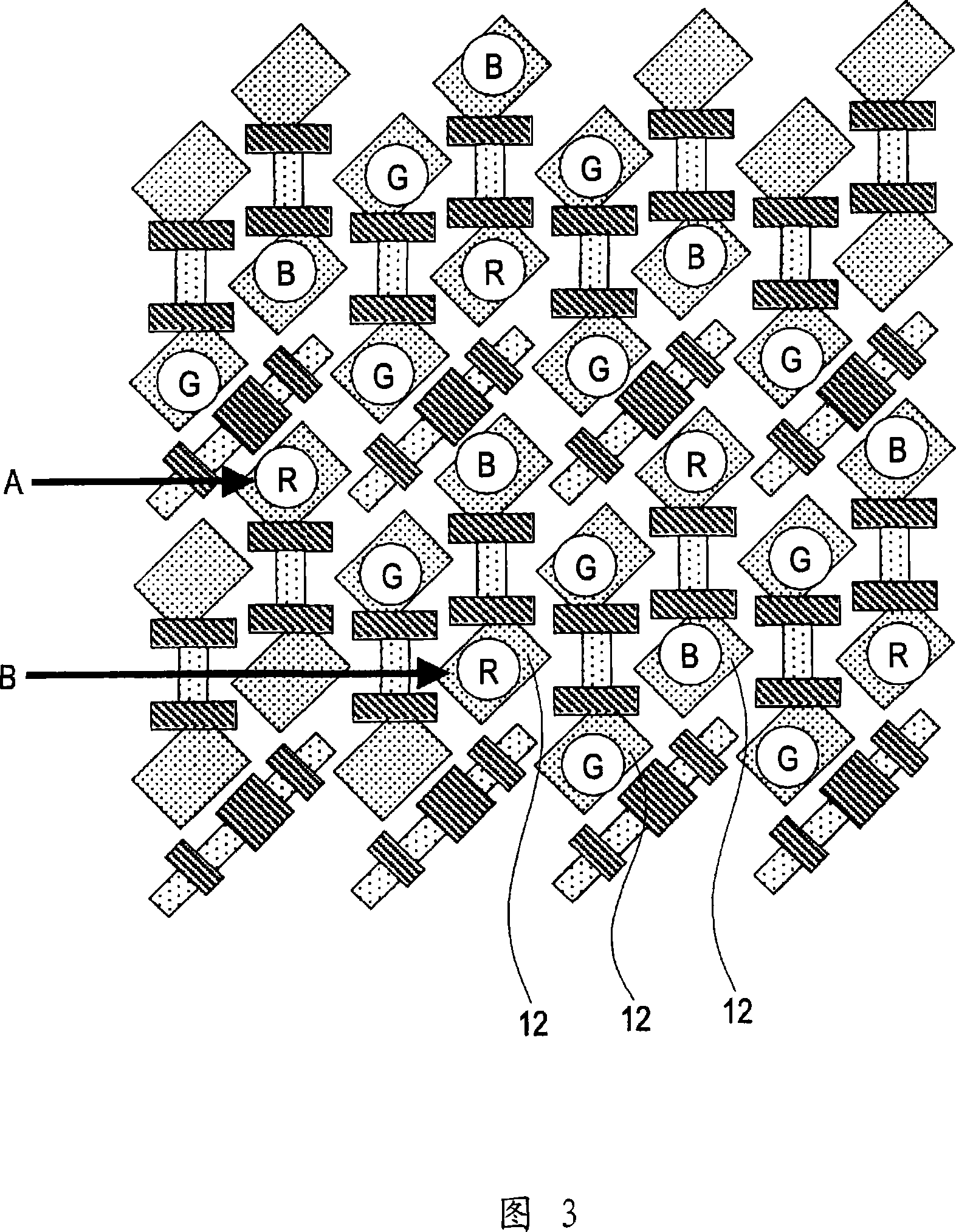

[0114] For the pixel array unit 2011, for example, pixel circuits 2010 are arranged in a matrix shape in a predetermined array pattern.

[0115] Moreover, for the pixel array unit 2011, each row of the vertical scanning circuit 2013 and the pixel array is connected to the reset line RSTL, the transfer selection line TRFL and the selection line SELL, and each row of th...

no. 4 example

[0172] The following description is about a layout example of a pixel circuit according to a fourth embodiment of the present invention. 13A and 13B are schematic diagrams illustrating one layout example of a pixel circuit according to a fourth embodiment of the present invention.

[0173] The pixel group GRP 2002 shown in FIG. 13A is an example in which the two pixel circuits shown in FIG. 9A share the source diffusion layer 2210a of the amplification transistor, and the two pixel circuits 2002a are arranged on the source diffusion layer of the amplification transistor. On the diagonal direction of 2210a. FIG. 13B is an equivalent circuit diagram of the pixel group GRP 2002 shown in FIG. 13A .

[0174] Pixel group GRP 2002 shown in FIG. 13B is an example in which two unit equivalent circuits 2002b shown in FIG. 13B share signal output terminal 2211b and are arranged in a diagonal direction of signal output terminal 2211b.

[0175] FIG. 14 is a schematic diagram in w...

no. 5 example

[0233] Next, a fifth embodiment of the present invention will be described with reference to the drawings. FIG. 16 is a block diagram illustrating one structural example of main units of an imaging apparatus according to a fifth embodiment of the present invention.

[0234] The imaging device 2001a includes a pixel circuit 2010, a pixel array unit 2011, a horizontal scanning circuit (HSCN) 2012a, an amplifier 2121, a vertical scanning circuit (VSCN) 2013, a signal processing circuit 2014, an analog-to-digital converter (A / D) 2015, a timing Adjustment unit 2016a, timing generator TG (2017) and lens 2018.

[0235] The timing adjustment unit 2016a is arranged inside the horizontal scanning circuit 2012a, delays the analog signal input from the pixel array unit 2011 through the amplifier 2121 by a predetermined time according to a predetermined program, and outputs it to the signal processing circuit 2014. The operation of the timing adjustment unit 2016 will be described b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More