Non-volatile memory and its manufacturing method

A non-volatile, manufacturing method technology, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problem of slow operation speed of storage units, low reading current of storage units, failure to improve component performance, etc. problem, to achieve the effect of reducing the size of the memory cell, large read current, and avoiding electrical penetration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

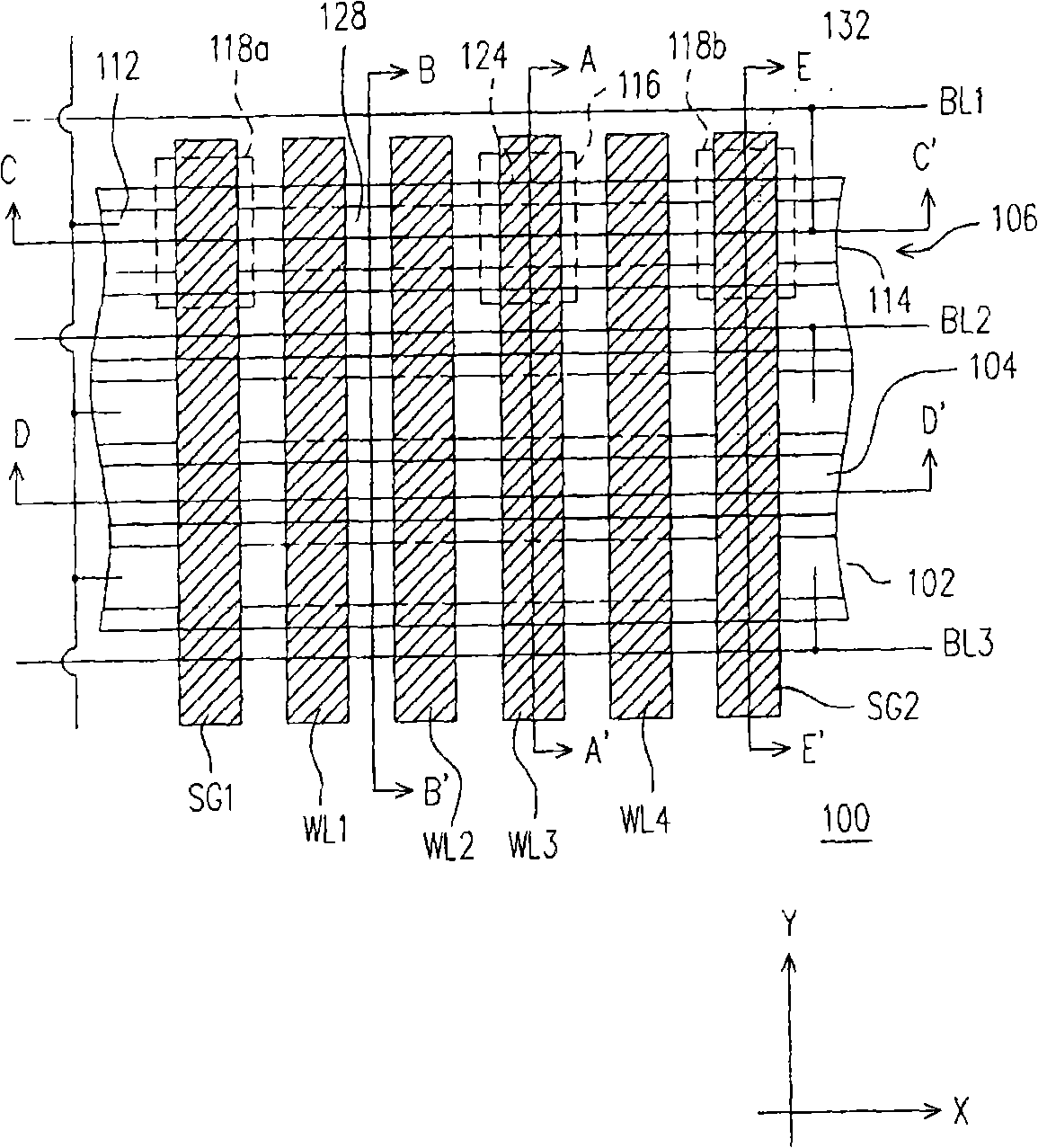

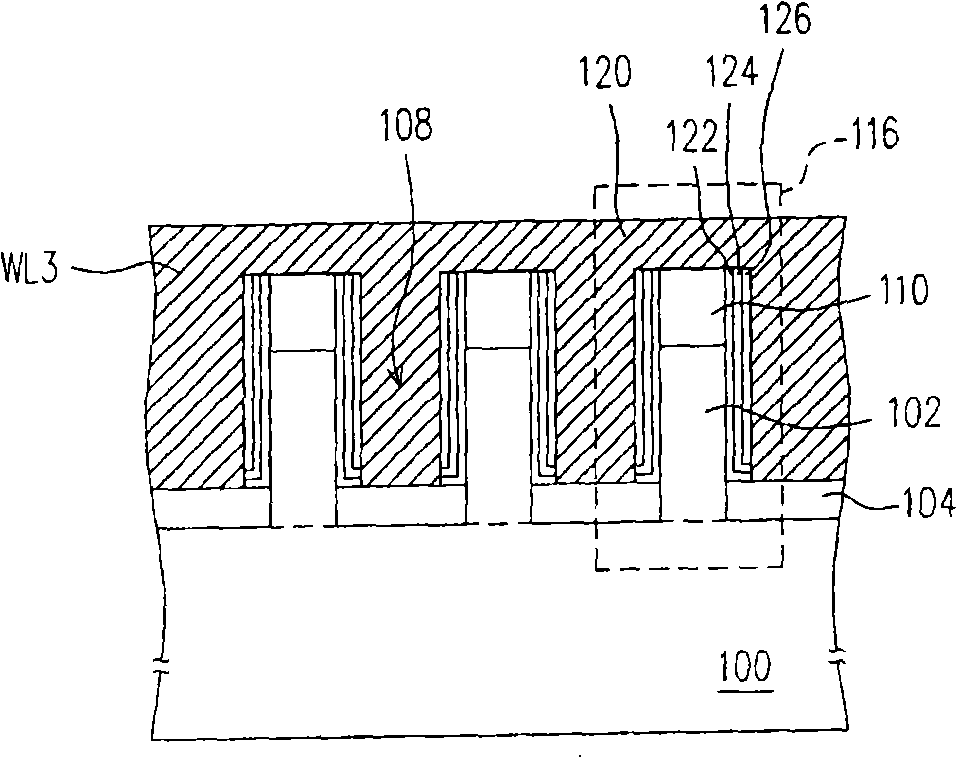

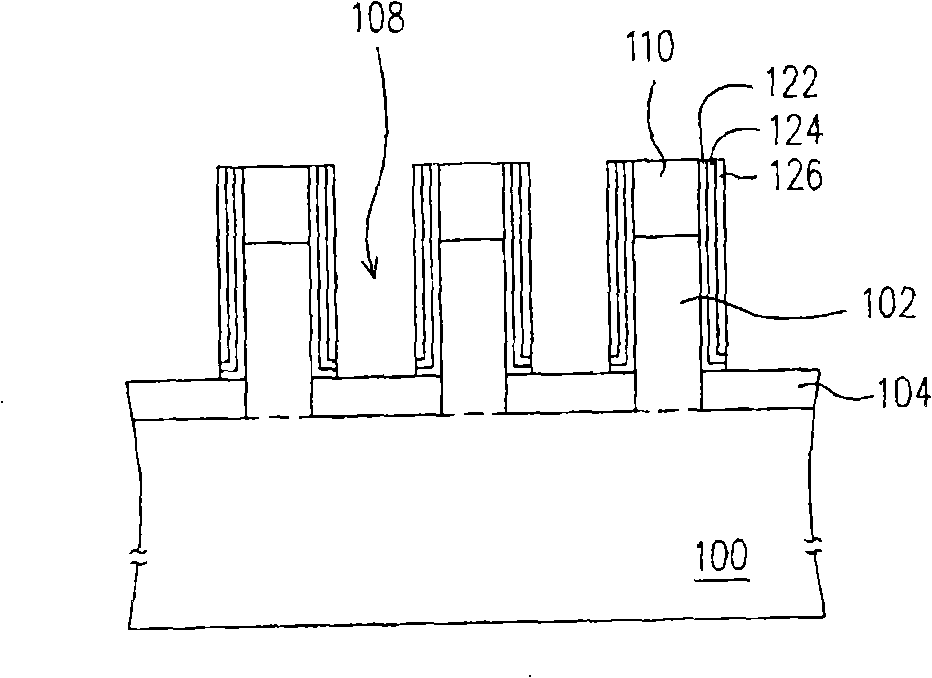

[0095] Figure 1A What is shown is a top view of a preferred embodiment of the non-volatile memory of the present invention. Figure 1B for depicted as Figure 1A Structural cross-section along line A-A'. Figure 1C for depicted as Figure 1A The structural cross-section along the line B-B' in the middle. Figure 1D for depicted as Figure 1A The structural cross-section along the C-C' line in the middle. Figure 1E for depicted as Figure 1A Structural cross-section along the line D-D'. Figure 1F for depicted as Figure 1A The structural cross-section along the E-E' line in the middle.

[0096] First, please refer to Figure 1A to Figure 1F , to illustrate the nonvolatile memory of the present invention. The nonvolatile memory of the present invention includes a substrate 100, multiple active layers 102, element isolation layers 104, multiple memory cell rows 106, multiple word lines WL1WL4, multiple bit lines BL1-BL3, and multiple source lines SL (only one is shown in ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More