Manufacturing method of gate

A manufacturing method and gate technology, applied in the field of gate manufacturing, can solve the problems of semiconductor device leakage current increase, gate sidewall surface roughness, roughness sensitivity, etc., to achieve reduced leakage current, reduced roughness, The effect of enhancing sensitivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0059] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0060] Figure 8 It is a flow chart of the first embodiment of the gate manufacturing method of the present invention.

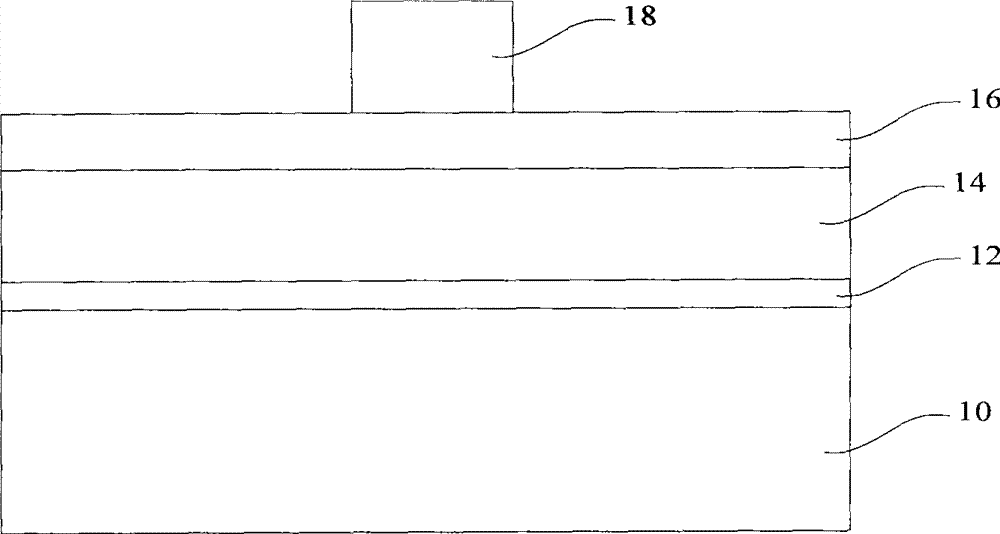

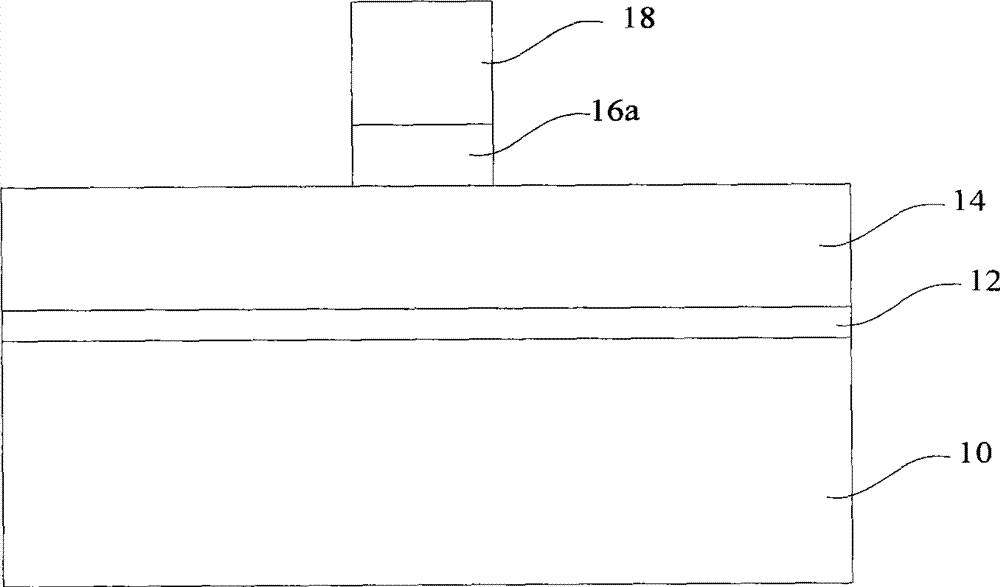

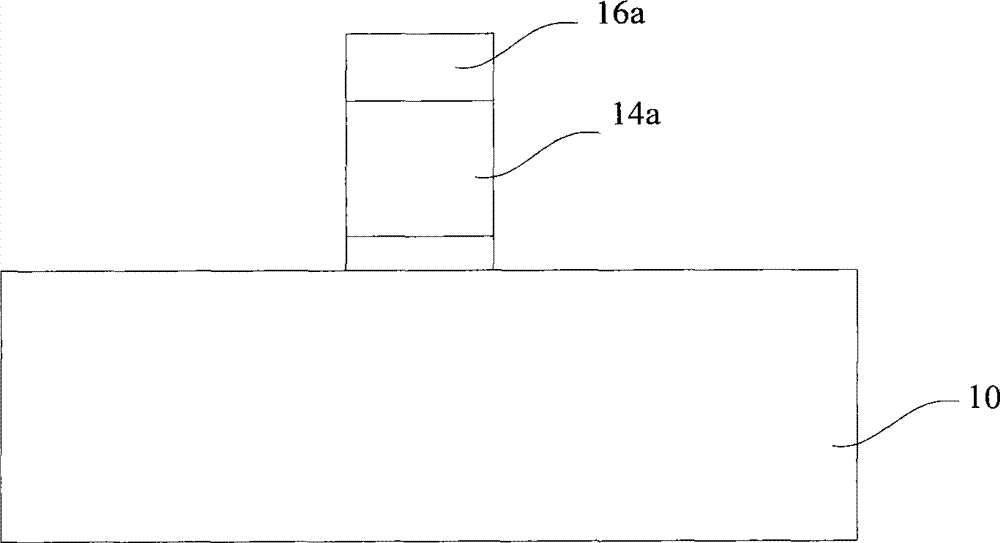

[0061] Such as Figure 8 The flow chart shown, step S100, provides a semiconductor substrate having a polysilicon layer thereon.

[0062] Such as Figure 9 The cross-sectional schematic diagram shown provides a semiconductor substrate 20, the material of the semiconductor substrate 20 can be one of single crystal silicon, polycrystalline silicon, and amorphous silicon, and the material of the semiconductor substrate 20 can also be a silicon germanium compound, The semiconductor substrate 20 may also be a silicon on insulator (Silicon On Insulator, SOI) structure or an epitaxial layer structure on silicon. N-type impurities or P-type impurities can be doped into the semiconductor substrate 20 to form N wells or P well...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More