Method for flattening medium surface in heterojunction bipolar transistor (HBT) process

A planarization and dielectric technology, which is applied in the field of compound semiconductor devices and integrated circuit manufacturing processes, can solve problems affecting device yields, and achieve the effects of avoiding instability, improving yields, and improving consistency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

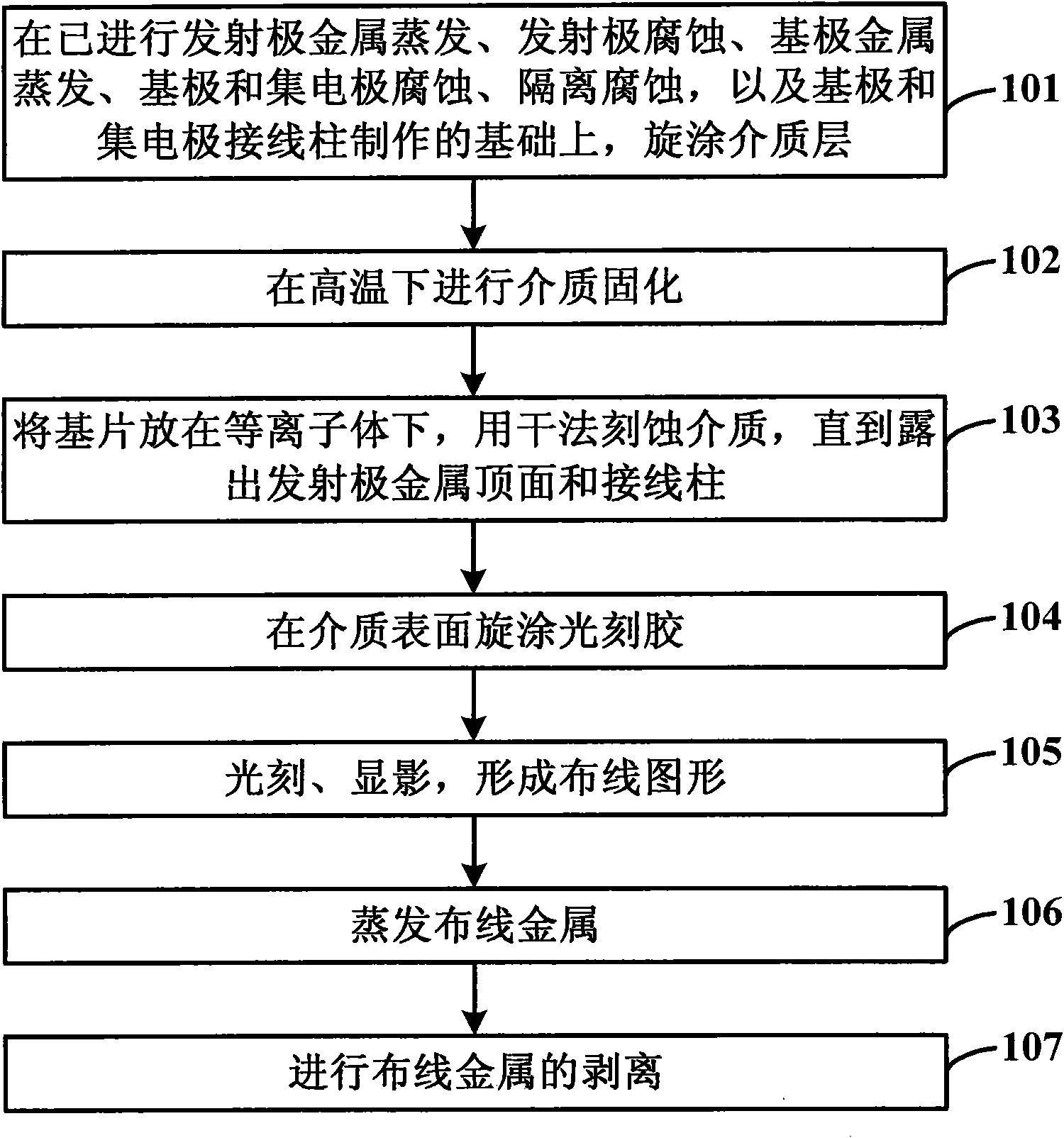

[0045] Such as figure 1 as shown, figure 1 The flow chart of the method for flattening the medium plane in the HBT process provided by the present invention, the method includes the following steps:

[0046] Step 101: spin coating a dielectric layer on the basis of the emitter metal evaporation, emitter corrosion, base metal evaporation, base and collector corrosion, isolation corrosion, and base and collector binding posts;

[0047] Step 102: performing medium curing at high temperature;

[0048] Step 103: Put the substrate under the plasma, etch the medium by dry method until the top surface of the emitter metal and the terminal are exposed;

[0049] Step 104: Spin-coat photoresist on the surface of the medium;

[0...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More