Laminated dielectric layer forming method and metal foredielectric layer forming method

A technology of metal front dielectric layer and dielectric layer, which is applied in the formation of metal front dielectric layer and the formation of laminated dielectric layer, can solve the problem of losing the tensile stress of the film layer, failing to meet the stress requirements, and the stress value of the metal front dielectric layer not meeting the design Requirements and other issues to achieve the effect of avoiding the influence of device thermal stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

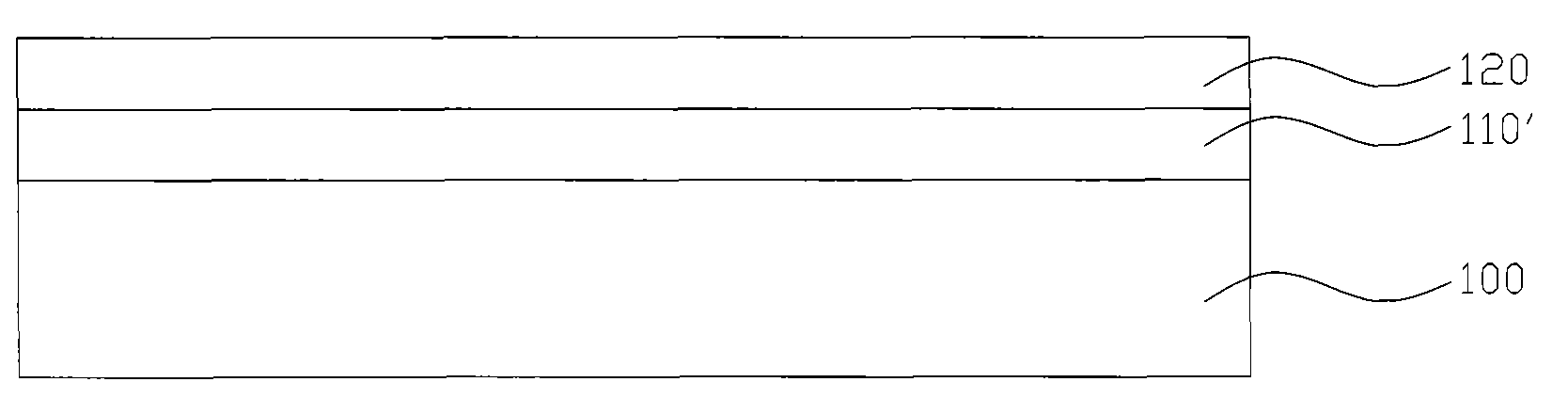

[0081] Figure 4 to Figure 8 It is a schematic diagram of the method for forming the pre-metal dielectric layer described in this embodiment. The pre-metal dielectric layer is a laminated dielectric layer composed of a first dielectric layer and a second dielectric layer on the first dielectric layer. Among them, the first dielectric layer adopts CVD process with good gap filling ability, especially for 65nm or below process, it is formed by HARP SACVD process; while the second dielectric layer adopts HDPCVD, PECVD or traditional SACVD with relatively high production capacity, etc. craft formation.

[0082] The reason why stacking dielectric layers are used to form the pre-metal dielectric layer is because as the feature size decreases, the aspect ratio of the gap becomes larger and larger. HDPCVD, PECVD or traditional SACVD processes can no longer satisfy the filling aspect ratio greater than The 7:1 gap requirement, and the HARP SACVD process has excellent gap filling abil...

Embodiment 2

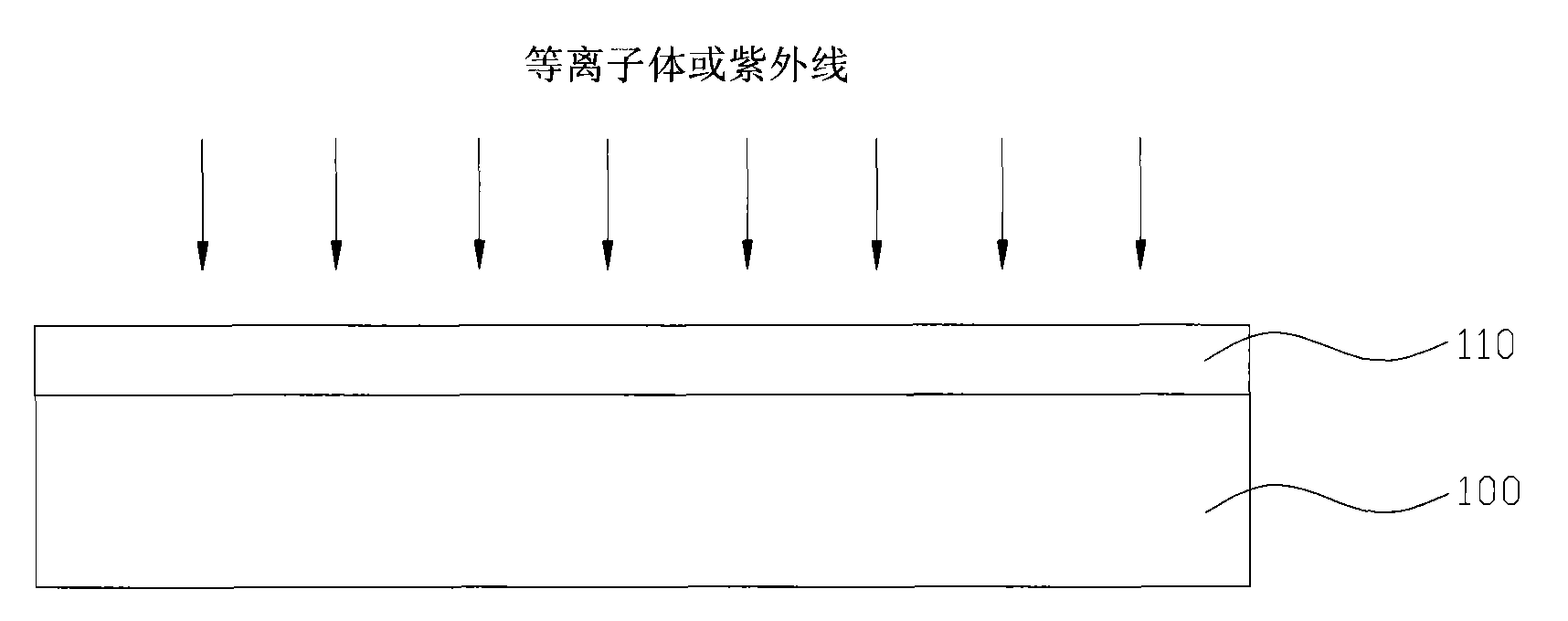

[0099] The difference between the method for forming the pre-metal dielectric layer in this embodiment and the first embodiment is that the first dielectric layer is dehumidified by ultraviolet irradiation in an oxygen-containing atmosphere.

[0100] Such as Figure 11 As shown, a gate 401 and a side wall 403 surrounding the gate are formed on a semiconductor substrate 400 with an active region through a front-end process, and a barrier layer 405 is formed, and then a first HARP SACVD process is used on the barrier layer 405. Dielectric layer 410 . The processes and materials used for the above-mentioned gate 401 , sidewall 403 , barrier layer 405 and first dielectric layer 410 are the same as those in Embodiment 1, and will not be repeated here.

[0101] Before forming the second dielectric layer, the first dielectric layer 410 is irradiated with ultraviolet rays in an oxygen-containing atmosphere to perform dehumidification treatment. The oxygen-containing atmosphere inclu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com