Hardware device and method for assisting in processing dynamic bandwidth allocation algorithm

A technology of dynamic bandwidth allocation and hardware device, which is applied to the selection device, selection device, electrical components and other directions of the multiplexing system. and practicality, performance improvement, area reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

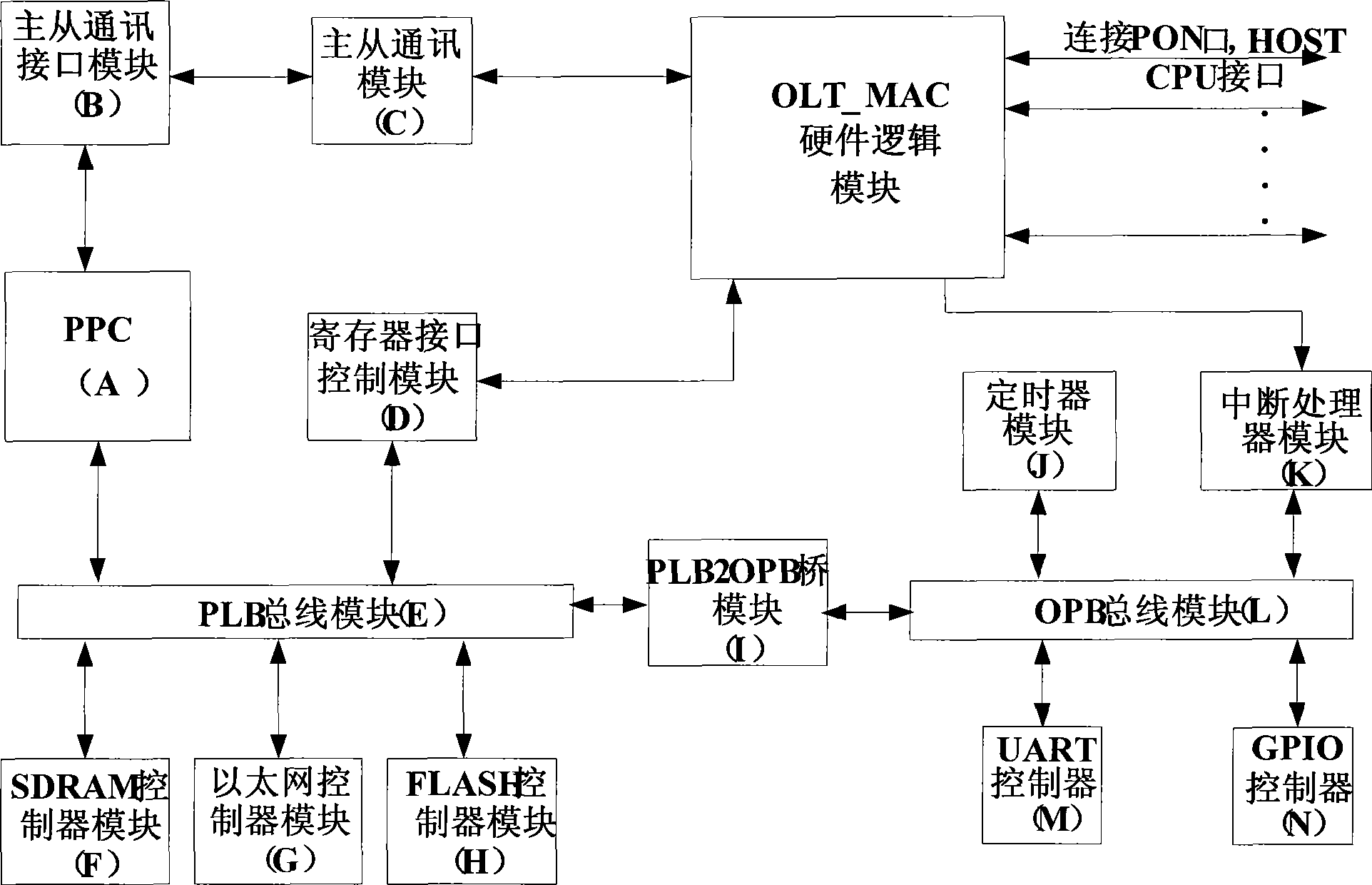

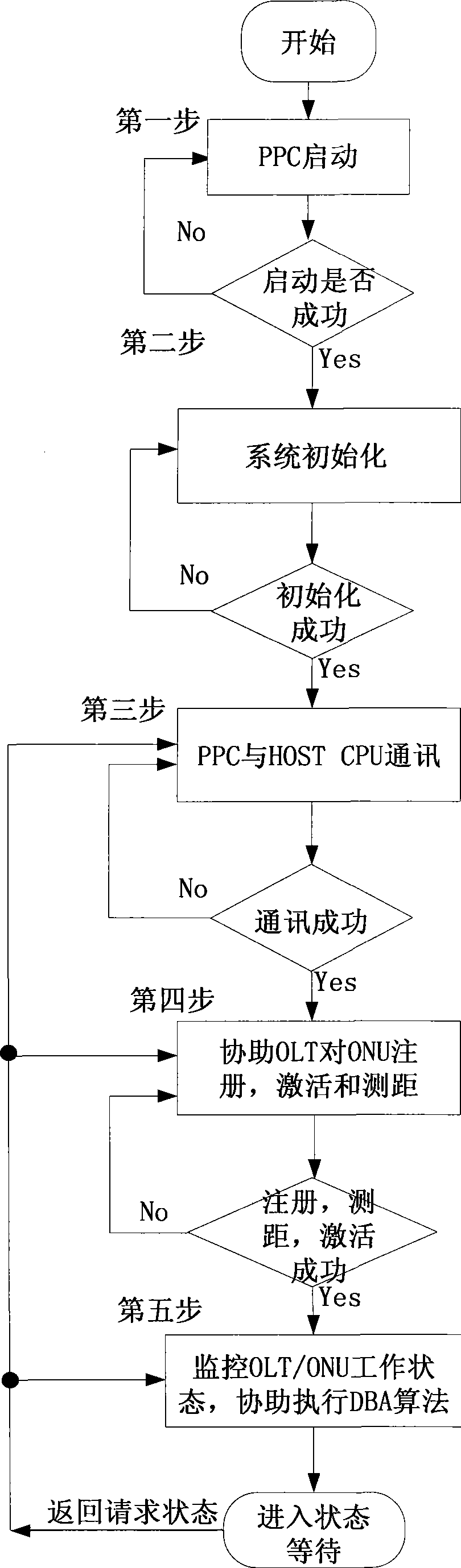

[0027] The present invention builds an embedded PowerPc CPU subsystem based on the embedded PowerPc405 (abbreviated as PPC) hard core in the XILINX V4 FX100FPGA. After the subsystem is powered on and completes boot (boot), it first initializes the system with the support of the operating system and software, completes the configuration and setting of the GPON OLT MAC, and completes the optical terminal side hardware logic module (OLT) The network unit (ONU) performs related configuration and initialization (including assisting in ranging, assisting in obtaining the S / N of the ONU, and setting the power of the ONU, etc.). After the system enters normal operation, it monitors the working status of OLT and ONU, assists in the processing of alarms and errors of OLT and ONU, and assists the hardware in the bandwidth allocation of the DBA algorithm of TCONT (Transmission Container) in the ONU. In addition, the PPC system also assists the OLT to complete the key exchange with the ONU...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More