LDMOS transistor structure and preparation method

A transistor and high-voltage technology, applied in the field of LDMOS transistor preparation, can solve the problems of increasing device area and cost, and achieve the effects of small product area, cost reduction, and design size reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

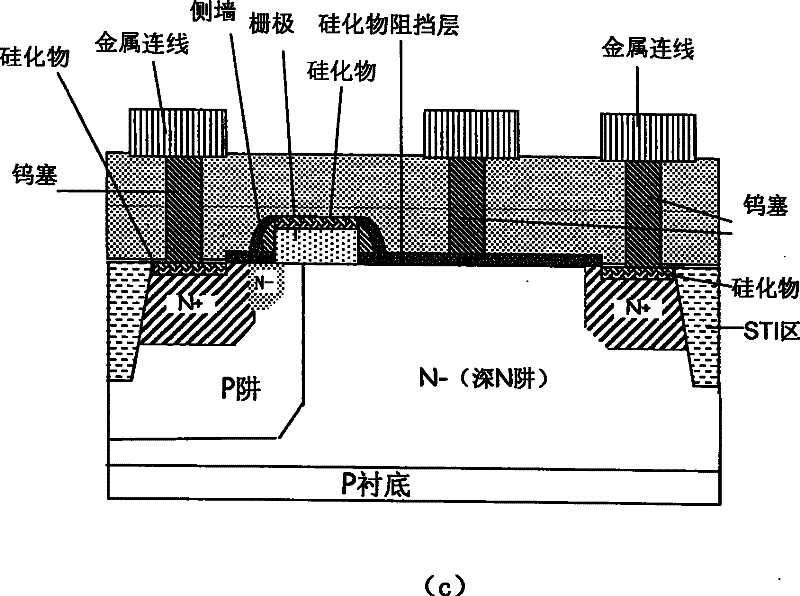

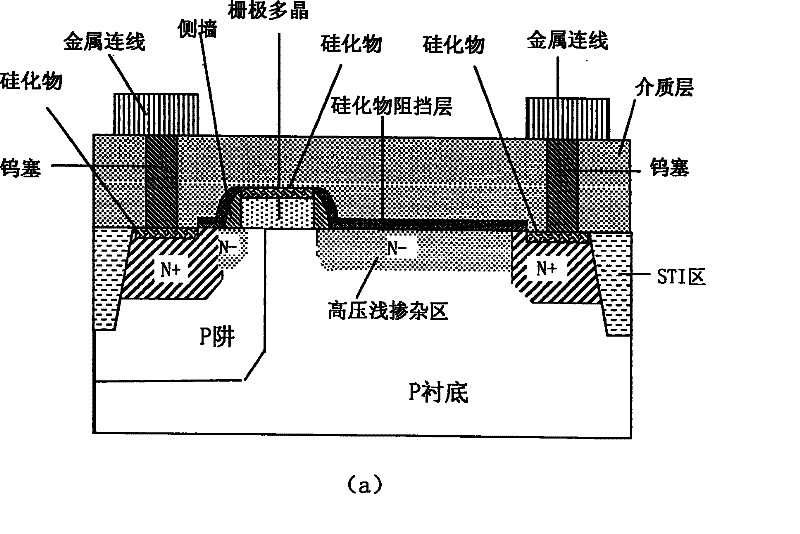

[0020] The LDMOS transistor structure of the present invention, starting from the electrical point of view, applies an electric field in the direction perpendicular to the level drop, so that the level drop line B has to turn under the action of the transverse electric field, thereby also achieving the purpose of increasing the level drop electric field.

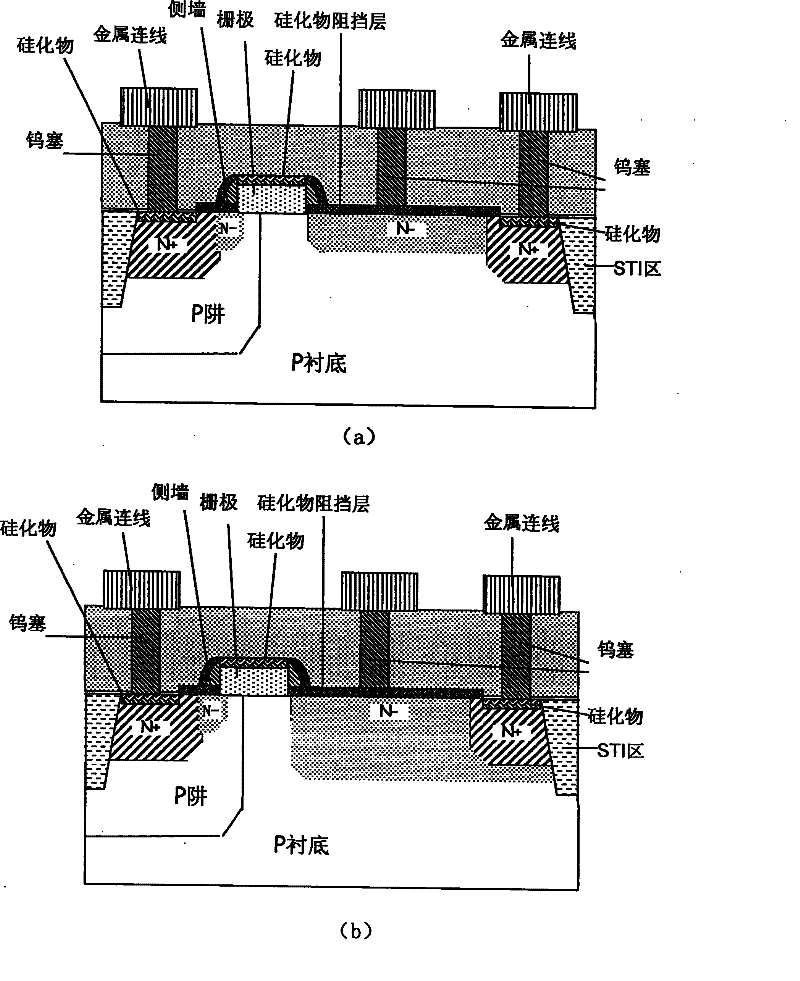

[0021] Such as Figure 7 (a) and Figure 7 As shown in (b), several contact holes or strip-shaped contact trenches are formed in the high-voltage shallow doped region (also called the withstand voltage region) of the traditional LDMOS device, and then the contact holes or contact trenches are filled with tungsten, and then Metal wiring is formed thereafter. The LDMOS transistor structure of the present invention includes a source heavily doped region, a source lightly doped region, a gate and gate sidewalls, a drain heavily doped region, and a silicon region on the side of the gate close to the drain to the drain. There is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More