Embedded programmable memory based on memory IP core

A technology of intellectual property core and memory, applied in the field of microelectronics, can solve the problems of long critical path, slow working speed, complicated design, etc., and achieve the effect of reducing timing critical path, improving working speed, and reducing propagation delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

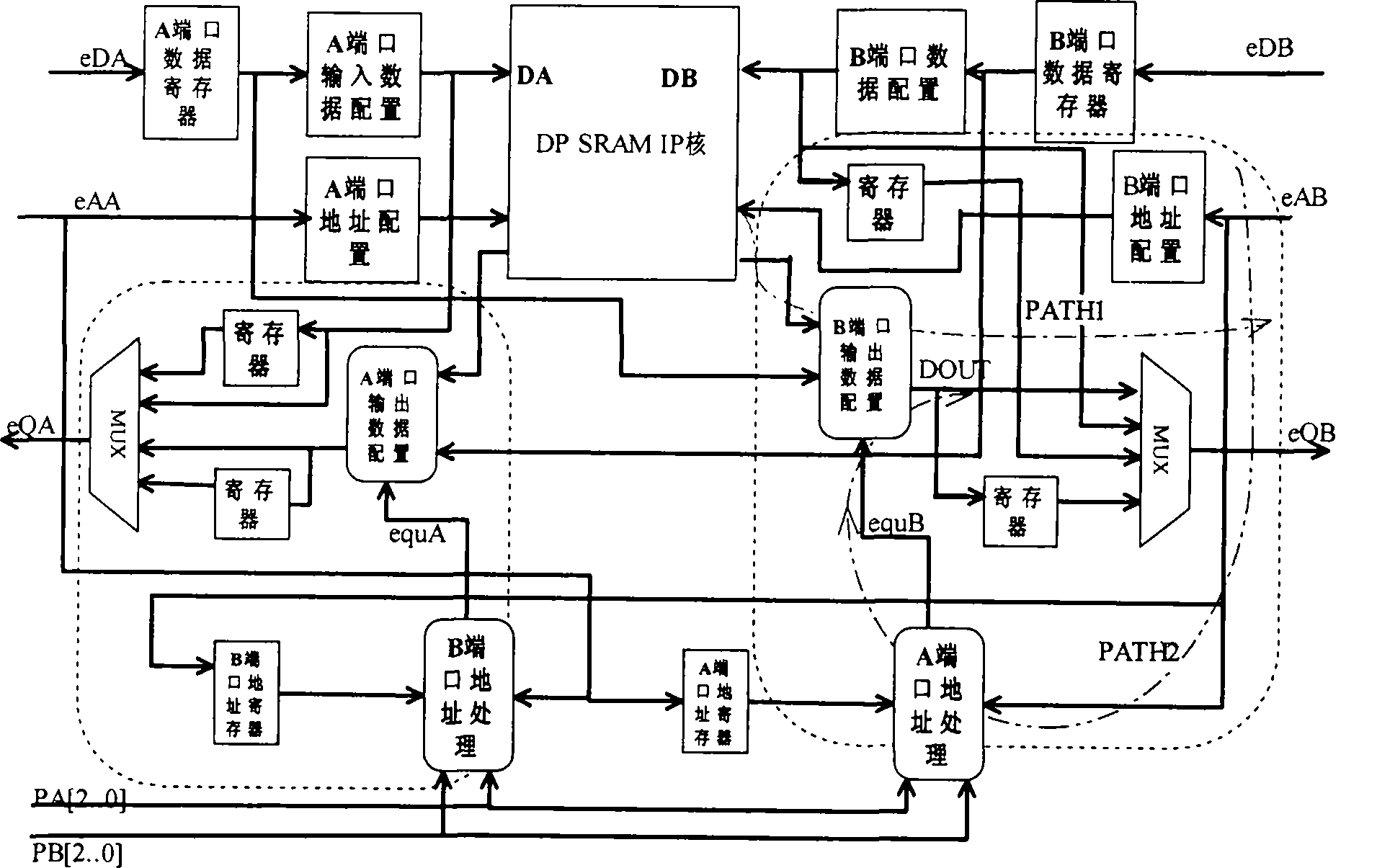

[0037] In order to make the objectives, technical solutions, and advantages of the present invention clearer, the following further describes the present invention in detail with reference to specific embodiments and drawings.

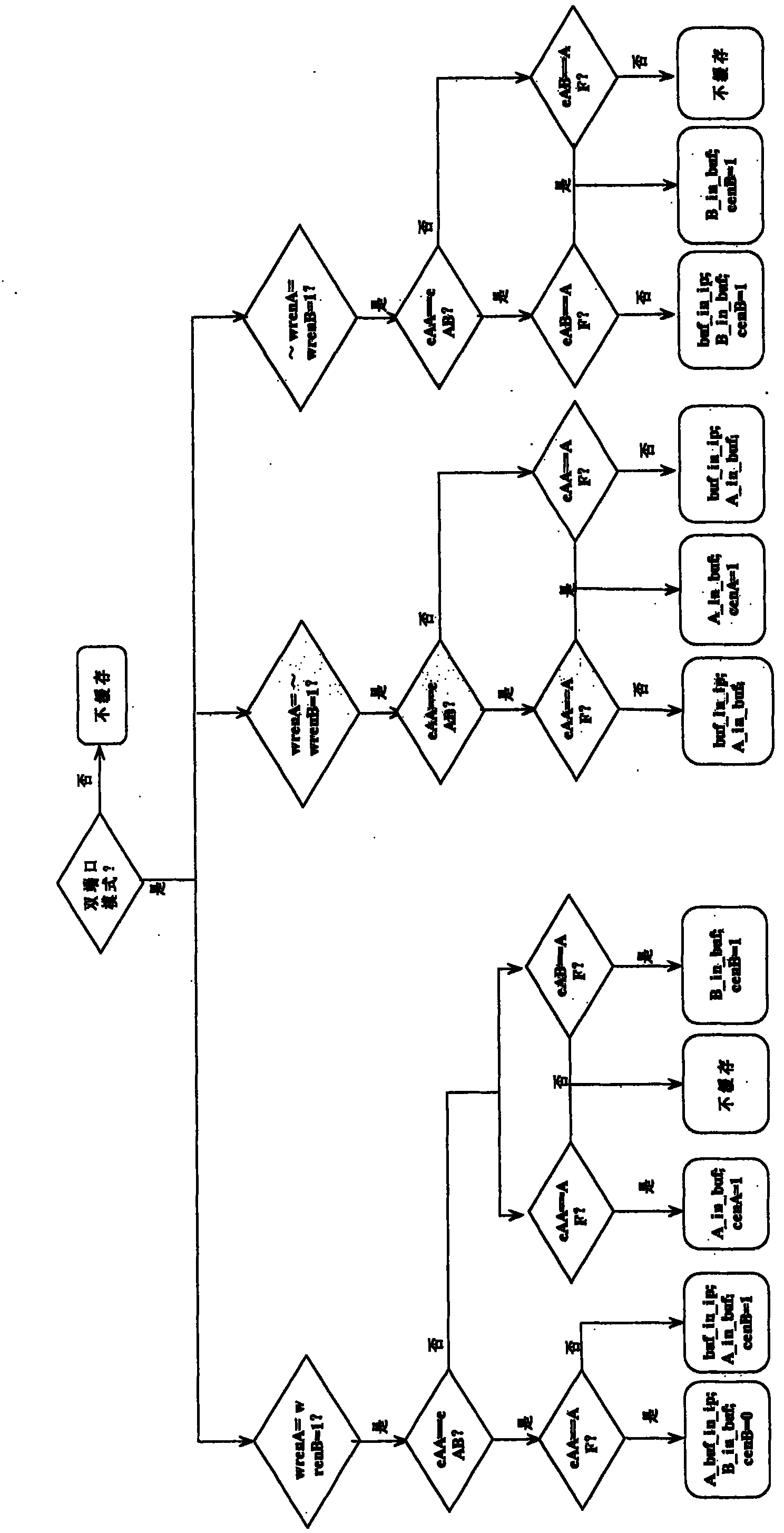

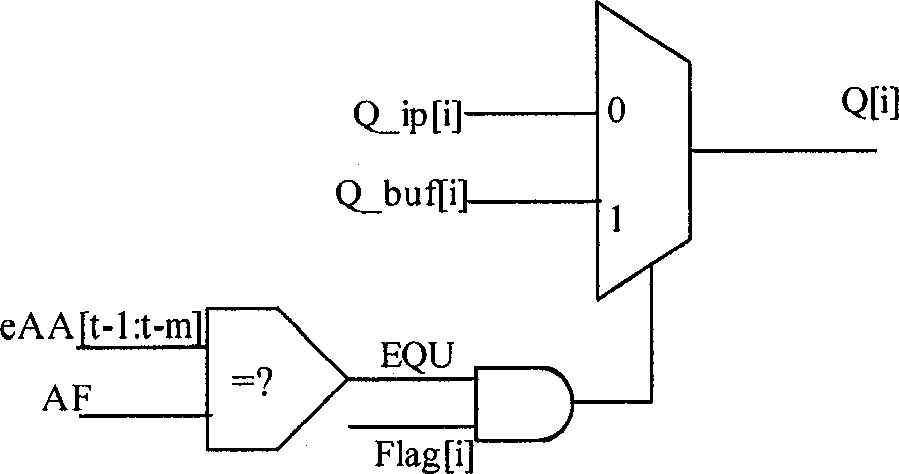

[0038] The core idea of the present invention is to use the added register to cache the conflicting data and addresses, the flag bit of the data bit, and the read-write conflict detection and protection mechanism to realize the programmable memory, which has both the simplicity of design and the Functional flexibility has made many extensions to conventional memory functions.

[0039] The present invention lists programmable parameters such as working mode and access bit width. These parameters are listed in the device manuals of some Field Programmable Gate Array (Field Programmable Gate Array, FPGA) (such as literature ) Has been described and does not belong to the present invention; but the present invention includes the realization mechanism of these...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More