MOS switching circuit with broadband and high linearity

A switching circuit and high linearity technology, applied in the field of MOS switching circuits, can solve the problems of high switching cost, inability to meet the use of advanced ADCs, and time-consuming startup, to achieve good signal linearity, eliminate non-ideal factors, and high noise-free The effect of scattered dynamic range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings.

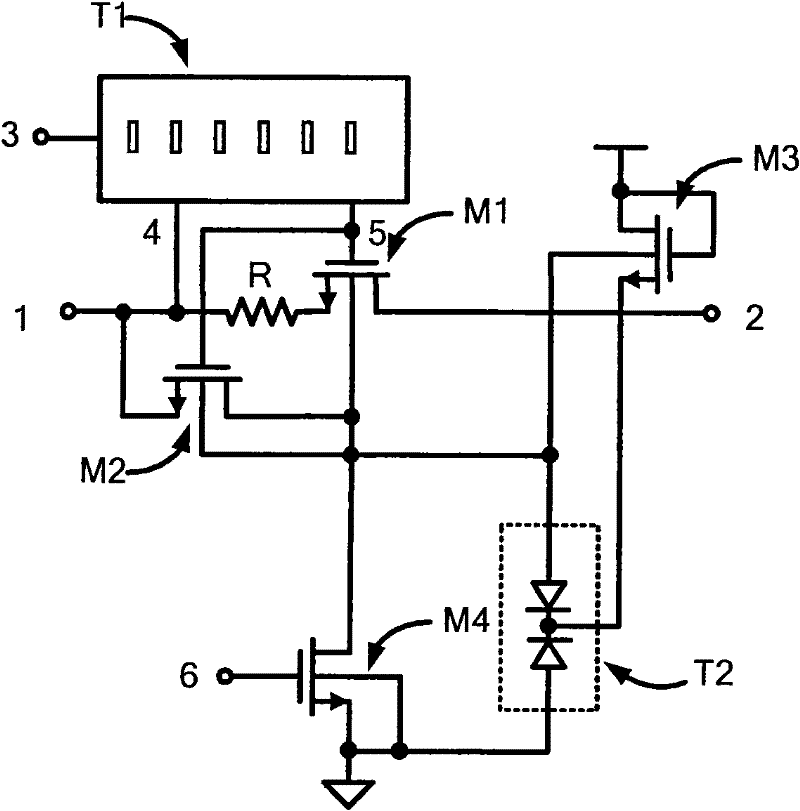

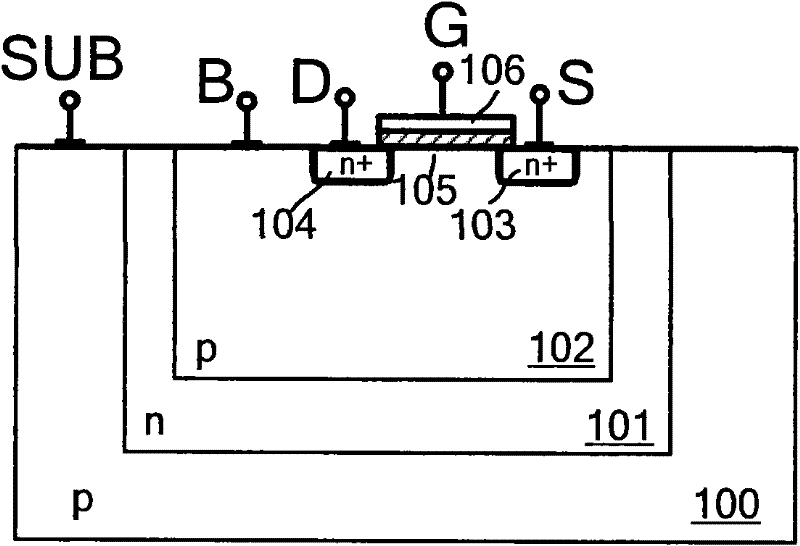

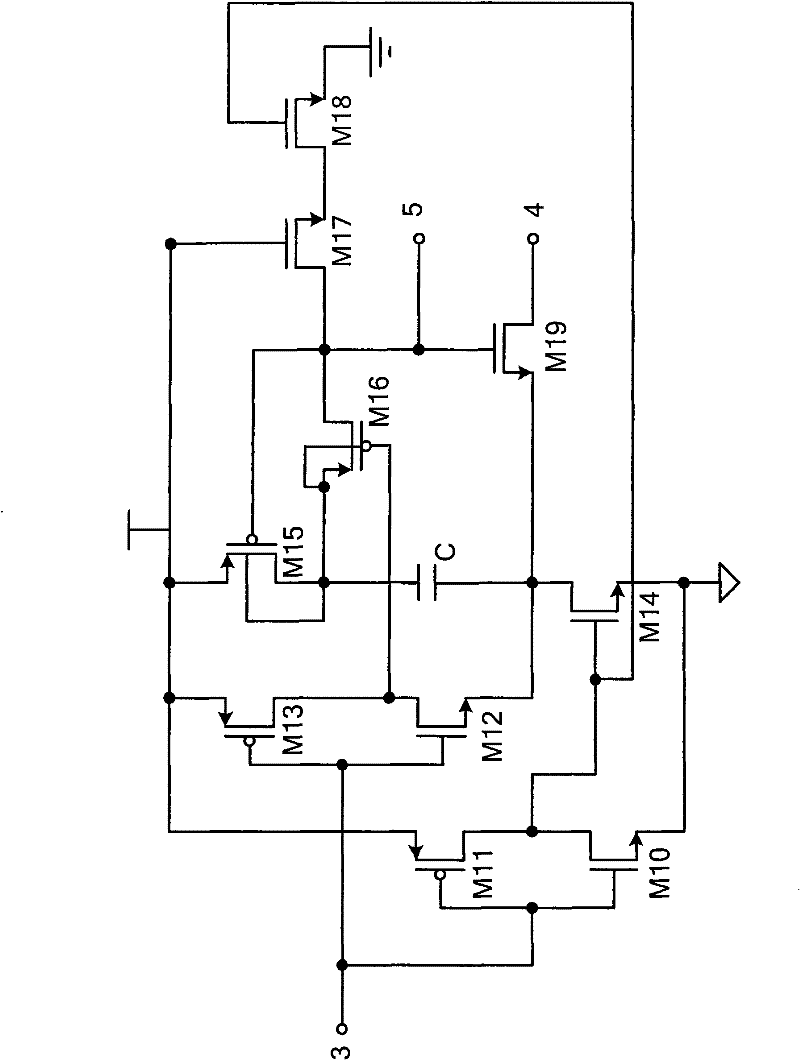

[0017] figure 1 A MOS switch circuit with wideband high linearity is shown as an embodiment of the present invention. Such as figure 1 As shown, it includes a first input terminal 1 and a first output terminal 2; a gate voltage bootstrap circuit T1 includes a first clock signal 3, a second input terminal 4 and a second output terminal 5; combined as figure 2 As shown in the schematic diagram of the structure of the MOS transistor, it can be seen that the p-type well region 102 forming the MOS transistor is arranged on the n-type deep well region 101, and the n-type deep well region 101 is arranged on the p-type substrate 100 above; the first enhancement MOS transistor M1 is formed in the first p-type well region, its source terminal is connected to the first in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More