Frequency compensation circuit applicable to high speed integrated amplifier

An integrated amplifier and frequency compensation technology, which is applied in the direction of improving the amplifier to reduce temperature/power supply voltage changes, etc., can solve the problems of integrated amplifier bandwidth expansion, CMOS circuit utility reduction, and frequency compensation weakening, so as to achieve easy layout matching and sensitivity The effect of reducing the speed and improving the stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0011] The present invention will be described in detail below with reference to the accompanying drawings.

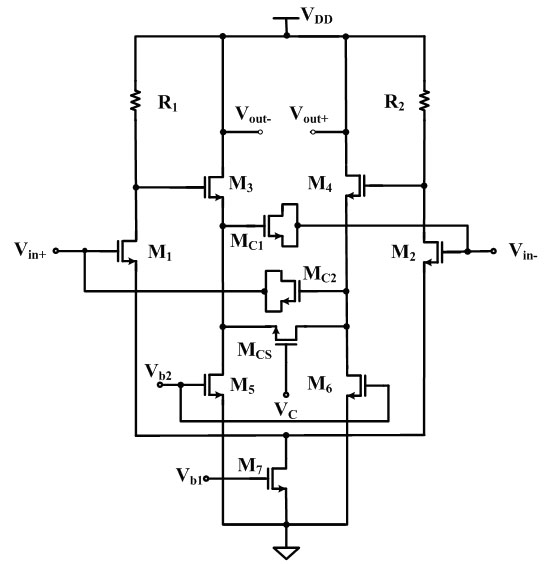

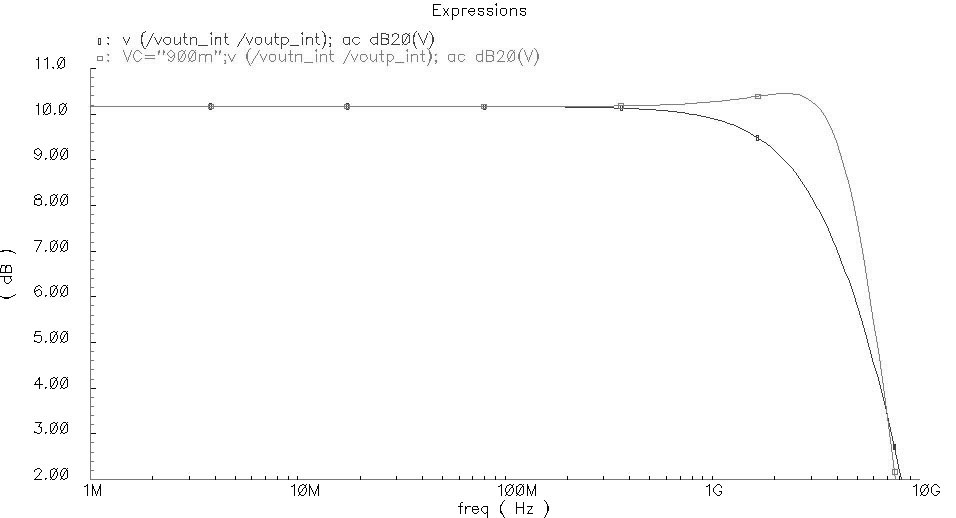

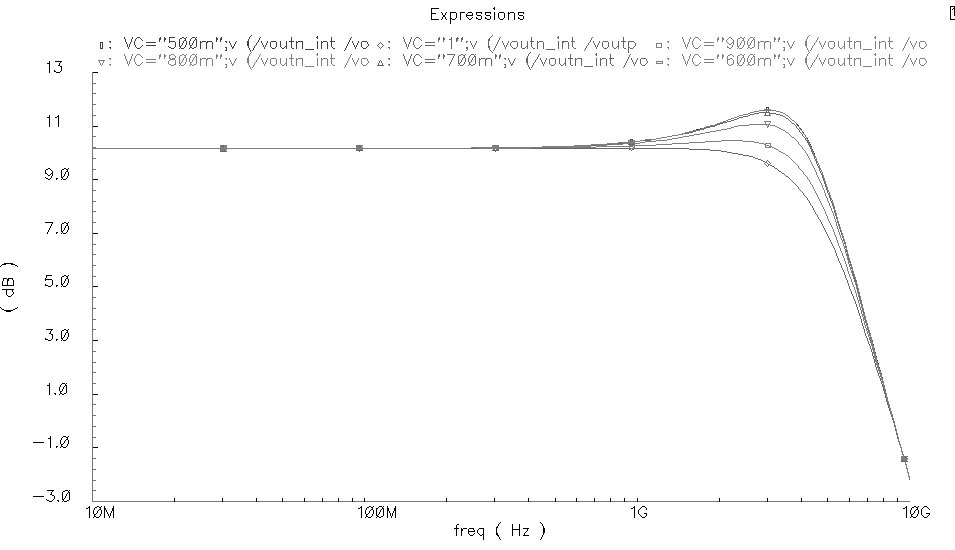

[0012] The present invention designs a frequency compensation circuit suitable for high-speed integrated amplifiers, and its basic application diagram is as follows figure 1 shown. The frequency compensation circuit is composed of a main stage amplifier and a frequency compensation circuit. Among them, the primary amplifier is a fully differential amplifier with a resistive load. The parasitic capacitance brought by the resistive load is smaller than that of the active load, which is suitable for high-frequency application circuits. The frequency compensation circuit consists of a source follower with variable gain and a pair of compensation capacitors. The input signal is applied to the main stage amplifier input MOS tube M 1 , M 2 at the gate terminal, the load resistor R at the drain terminal 1 , R 2 Generate a voltage signal output on. MOS tube M 3 ~M 6 C...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More