Wafer level chip scale packaging structure with low substrate resistance and manufacturing method thereof

A wafer-level chip and substrate resistance technology, used in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems such as wafer breakage, affecting chip performance, and inability to function, achieving low manufacturing costs and reducing Substrate resistance, easy operation effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

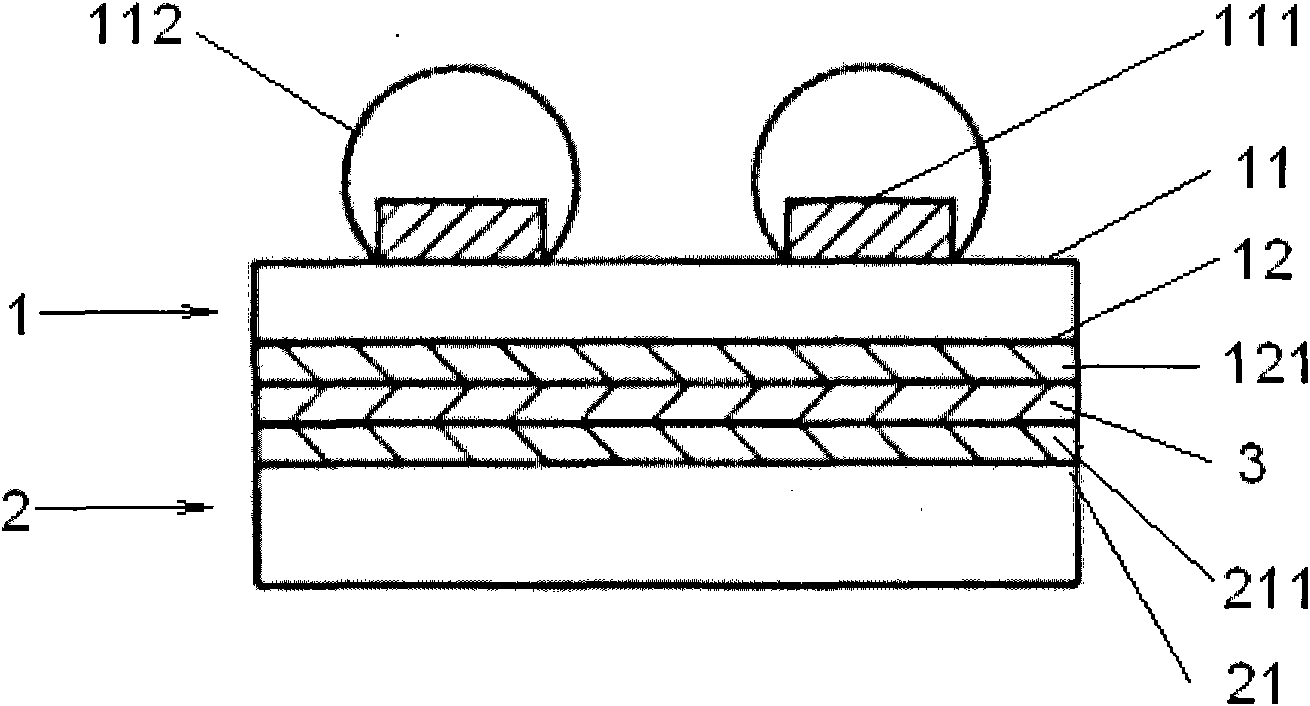

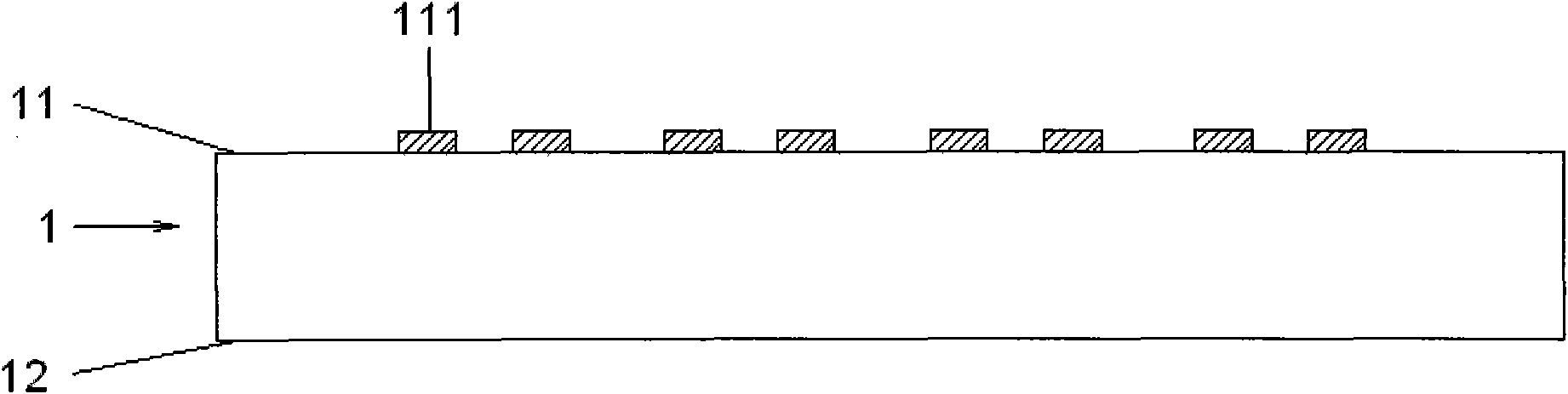

[0061] Example 1, please refer to the attached figure 2 As shown, a wafer-level chip size package with low substrate resistance includes a semiconductor chip 1 and a conductive reinforcement 2. The semiconductor chip 1 includes a semiconductor chip upper surface 11 and a semiconductor chip lower surface 12. On the semiconductor chip The surface 11 is provided with a plurality of integrated circuit chips (not shown in the figure), a plurality of UBM layers 111 and a plurality of solder balls 112 for chip connection on each UBM layer 111, The lower surface 12 of the semiconductor wafer is provided with a second metal layer 121; the conductive reinforcement 2 includes an upper surface 21 of the conductive reinforcement, and the upper surface 21 of the conductive reinforcement is provided with a first metal layer 211; the first metal layer 211 and the second metal A conductive epoxy resin 3 is provided between the layers 121 , and the first metal 211 and the second metal 121 are ...

Embodiment 2

[0063] Example 2, please refer to the attached Figure 11 As shown, a wafer-level chip-scale package with low substrate resistance includes a semiconductor chip 1' and a conductive reinforcement 2', and the semiconductor chip 1' includes a semiconductor chip upper surface 11' and a semiconductor chip lower surface 12 ', the upper surface 11' of the semiconductor wafer is provided with a plurality of integrated circuit chips (not shown in the figure), a plurality of under-bump metallization layers 111' and a chip for chip on each under-bump metallization layer 111' A plurality of solder balls 112' connected, the lower surface 12' of the semiconductor wafer is provided with a second metal layer 121'; the conductive reinforcement 2' includes an upper surface 21' of a conductive reinforcement, and the upper surface 21' of the conductive reinforcement is provided with a first The metal layer 211'; the first metal layer 211' is glued together with the second, so that the semiconduct...

Embodiment 3

[0065] Embodiment 3. In this embodiment, the structure of the wafer-level chip size package with low substrate resistance is the same as that of Embodiment 1, and the process is basically the same. The difference is that the first metal layer and the The second metal layer is two mutually fusible metals, so there is no need for the connection of solder. At high temperature, the two metals can be fused together, so that the conductive reinforcement and the semiconductor chip are combined together, with low The substrate lateral resistance. Preferably, the two mutually fusible metals are Au and Sn, respectively.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More