High-performance semiconductor device and manufacturing method thereof

A technology of semiconductors and devices, which is applied in the field of high-performance semiconductor devices and their manufacturing, and can solve problems such as device performance degradation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

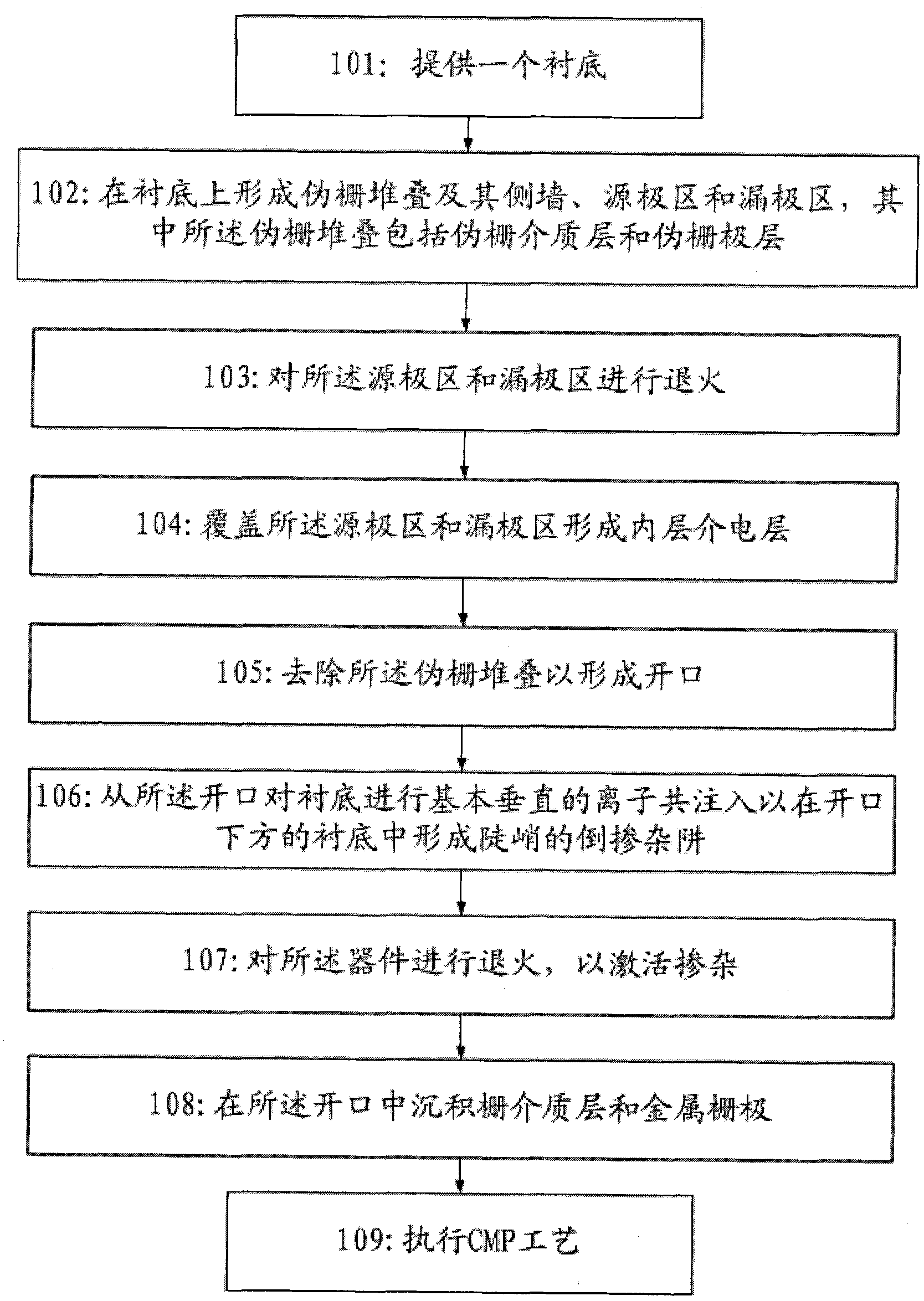

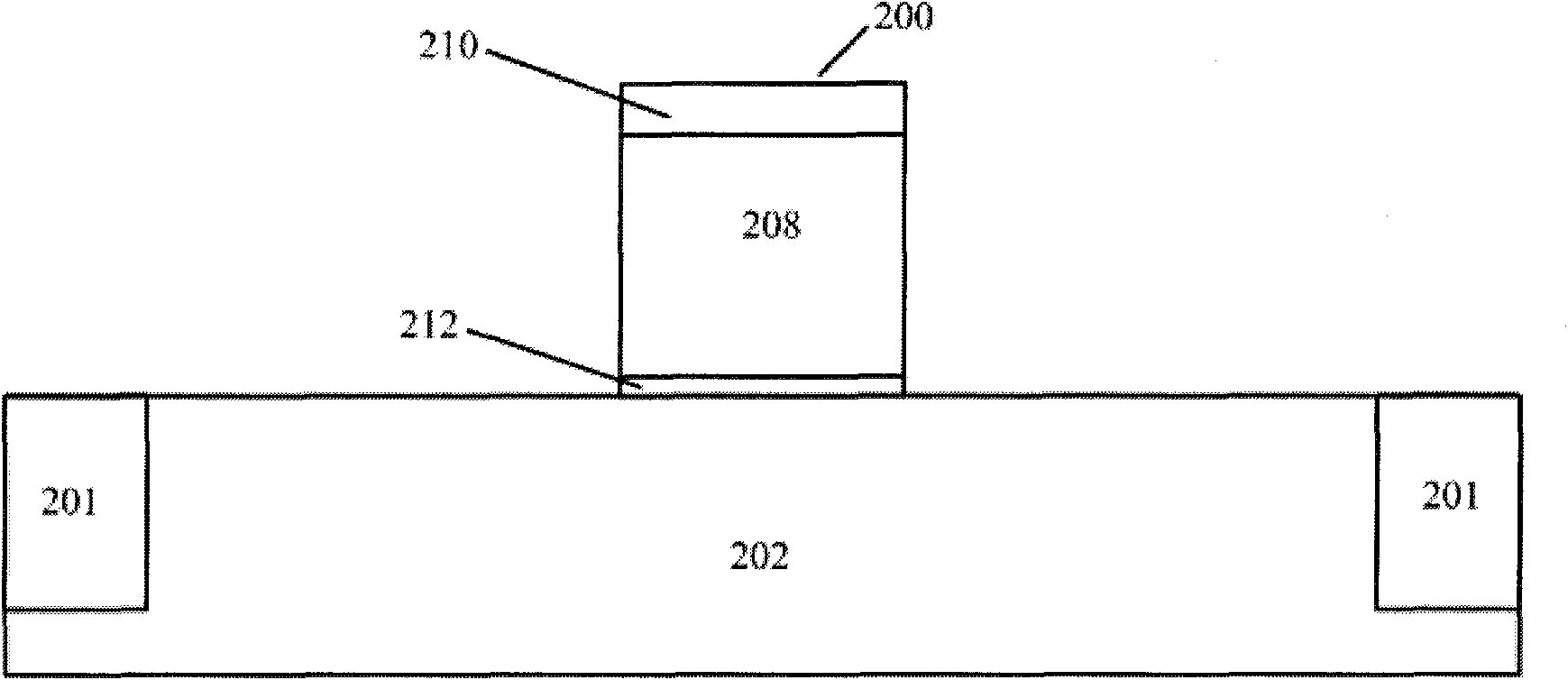

[0020] refer to figure 1 , figure 1 A flowchart showing a method of manufacturing a semiconductor device according to an embodiment of the present invention. In step 101, first provide a semiconductor substrate 202, refer to figure 2 . In this embodiment, the substrate 202 includes a silicon substrate (such as a wafer) in a crystal structure and an isolation region 201 . The substrate 202 may include various doping configurations according to design requirements known in the art (eg, p-type substrate or n-type substrate). Other example substrates 202 may also include other basic semiconductors, such as germanium and diamond. Alternatively, the substrate 202 may include a compound semiconductor, such as silicon carbide, gallium arsenide, indium arsenide, or indium phosphide. Furthermore, substrate 202 may optionally include epitaxial layers, may be altered by stress to enhance performance, and may include a silicon-on-insulator (SOI) structure.

[0021] In step 102, as ...

no. 2 example

[0034] Only the aspects of the second embodiment that differs from the first embodiment will be described below. Parts not described should be considered to be performed by the same steps, methods or processes as those in the first embodiment, and thus will not be described again. In the flow chart according to the second implementation of the present invention such as Figure 12 as shown in Figure 12 As shown, in step 206 , the substrate 202 is co-implanted with oblique angle ions from the opening to form steep ion implantation regions 207 near the source region and the drain region respectively. The ion co-implantation depth range of the oblique angle is about 5-500nm. The co-implantation of ions at an oblique angle to the substrate 202 from the opening can be carried out in the following manner: performing the first oblique angle ion implantation, and implanting the first dopant into the substrate 202 to form the first dopant in the source region and the drain electrode ...

no. 3 example

[0038] Only the aspects of the third embodiment that differs from the first embodiment will be described below. Parts not described should be considered to be performed by the same steps, methods or processes as those in the first embodiment, and thus will not be described again. In the flow chart according to the third implementation of the present invention such as Figure 16 as shown in Figure 16 As shown, in step 306, substantially vertical ion co-implantation and oblique angle ion co-implantation are performed on the substrate 202 from the opening, thereby forming a steep retrograde well 206 in the substrate 202 below the opening and respectively Steep ion implantation regions 207 are formed near the source and drain regions 204 . The depth range of the substantially vertical ion co-implantation and oblique angle ion co-implantation is about 5-500 nm.

[0039] The substantially vertical ion co-implantation and oblique angle ion co-implantation can be performed in the ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More