Method for manufacturing groove type longitudinal semiconductor device

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of difficulty in accurately controlling the height of silicon dioxide, increasing process complexity, and small process tolerance, achieving low cost, Improved dynamic characteristics, the effect of a simple method

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

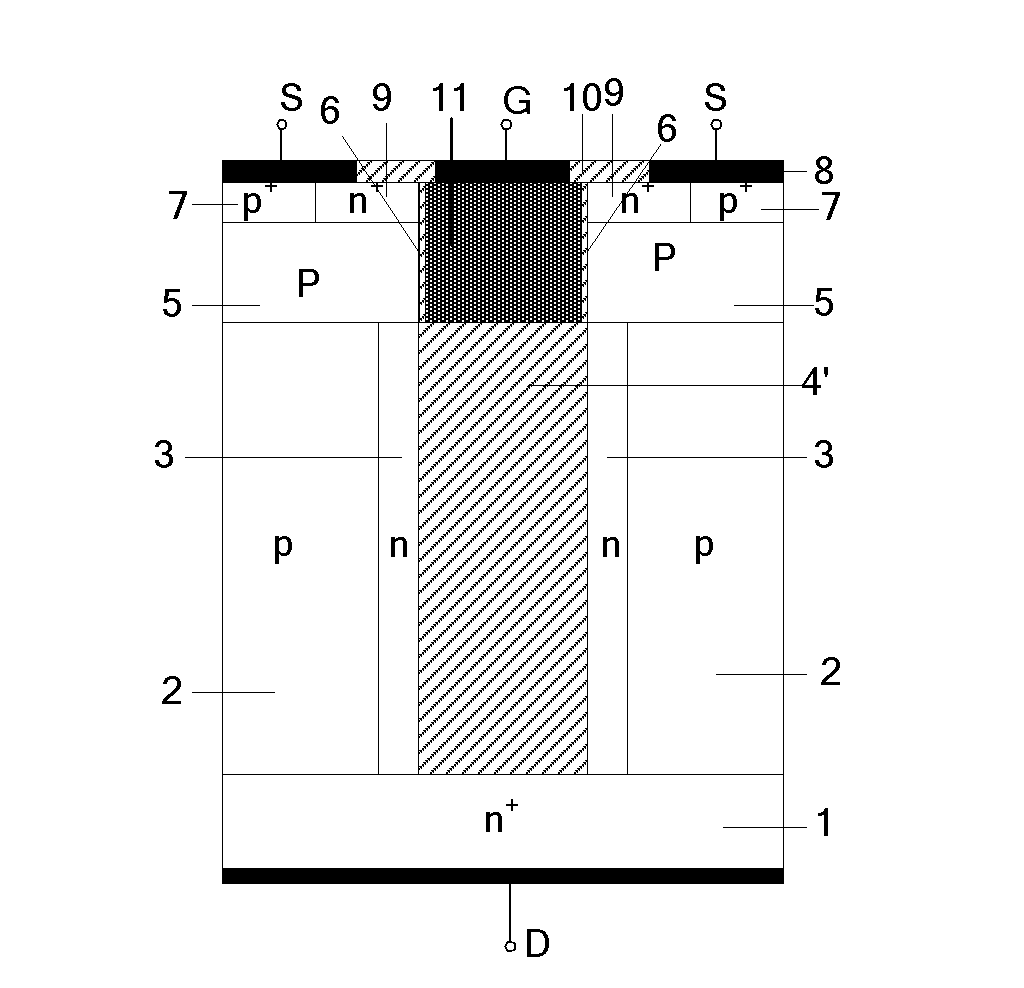

[0067] As a preferred embodiment of the present invention, the present invention discloses a novel superjunction semiconductor device structure (such as Figure 4h Shown) the manufacture method, it comprises the steps:

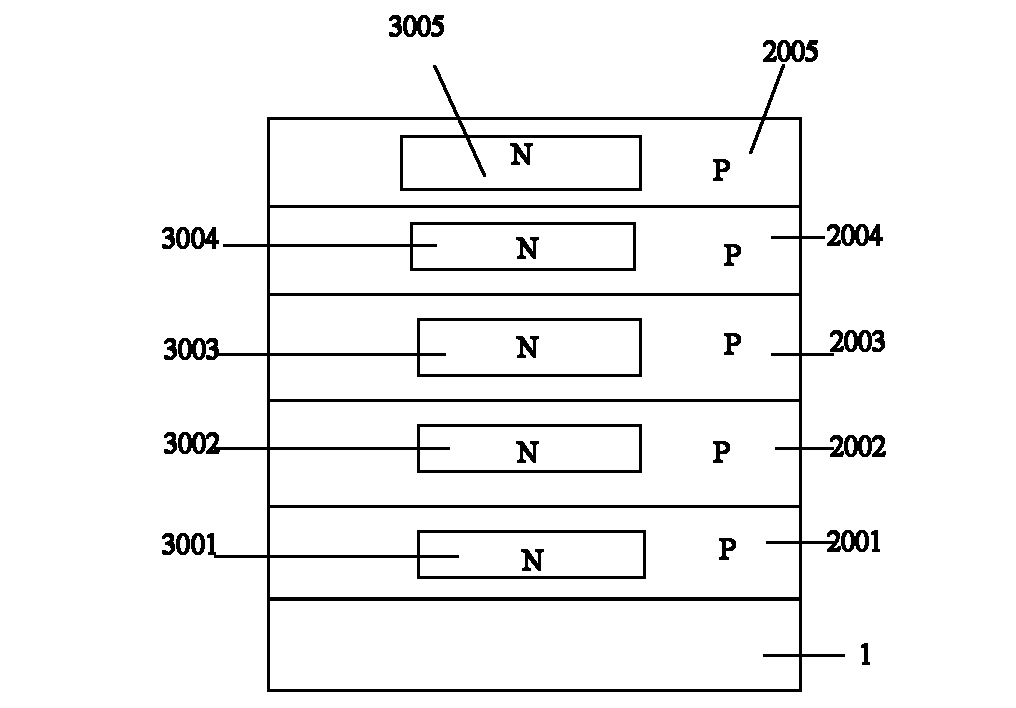

[0068] a, in the semiconductor substrate 1 (in this embodiment is n + epitaxially forming a first semiconductor drift region 2 on a type semiconductor substrate);

[0069] b. On the first semiconductor drift region 2, partially etch the first semiconductor drift region 2 up to the semiconductor substrate to form a first trench, such as Figure 4a shown.

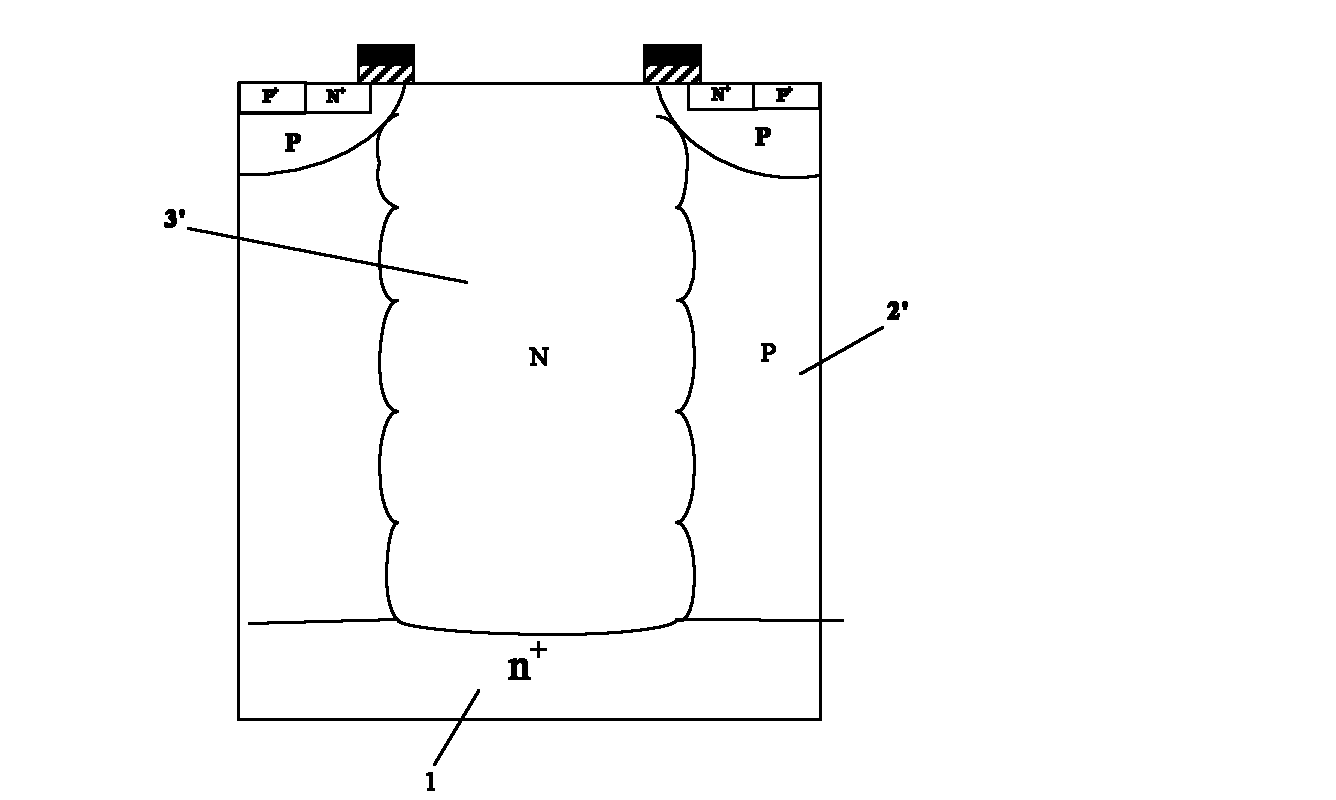

[0070] c. Growing a diffusion mask layer 14 on the back side of the semiconductor substrate and the top of the first semiconductor drift region 2, such as Figure 4b Shown; impurity diffusion and annealing are then performed to form the second semiconductor drift region 3 on the trench wall; the diffusion masking layer 14 is removed, as Figure 4cshown; the first semiconductor drift region and the second ...

Embodiment 2

[0084] The manufacturing process of the semiconductor device of the present invention described in Embodiment 1 is preferably applied to a MOS control vertical device, so as to alleviate the contradictory relationship among withstand voltage, on-resistance and switching loss. Applied in such as Figure 5a when the IGBT device shown. The difference from Example 1 is that the initial semiconductor material substrate 1 is P + The conductivity type of the semiconductor substrate 101 is the same as that of the first semiconductor drift region. Its key steps are as Figure 5b and Figure 5c shown. All the other steps are identical to Example 1.

Embodiment 3

[0086] The manufacturing process of the semiconductor device of the present invention described in Embodiment 1 can be applied to control vertical devices of N-channel MOS, and can also be applied to control vertical devices of P-channel MOS. P-channel VDMOS as Figure 6a shown. When used in the manufacture of P-channel MOS control vertical devices, the semiconductor substrate 1, the first semiconductor drift region 2, the second semiconductor drift region 3 formed by diffusion, the active region 5, the body contact region 7, the source region 9 and the N The channel MOS controls the doping type of the corresponding region of the vertical device. The key steps are as follows: Figure 6b and Figure 6c shown. In Embodiment 1, an N-channel VDMOS is manufactured, and N-type impurities are diffused on the trench sidewall of the P-type first semiconductor drift region 2 to form a second semiconductor drift region 3; in this embodiment, a P-channel VDMOS is manufactured, The sec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More