Manufacturing method of cold metal oxide semiconductor (MOS) super-junction structure and cold MOS super-junction structure

A manufacturing method and N-type technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of uneven bonding surface of super junction structure, and achieve the goal of overcoming uneven bonding surface, good controllability, reducing The effect of manufacturing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be further described below in conjunction with specific embodiments and accompanying drawings, but the protection scope of the present invention should not be limited thereby.

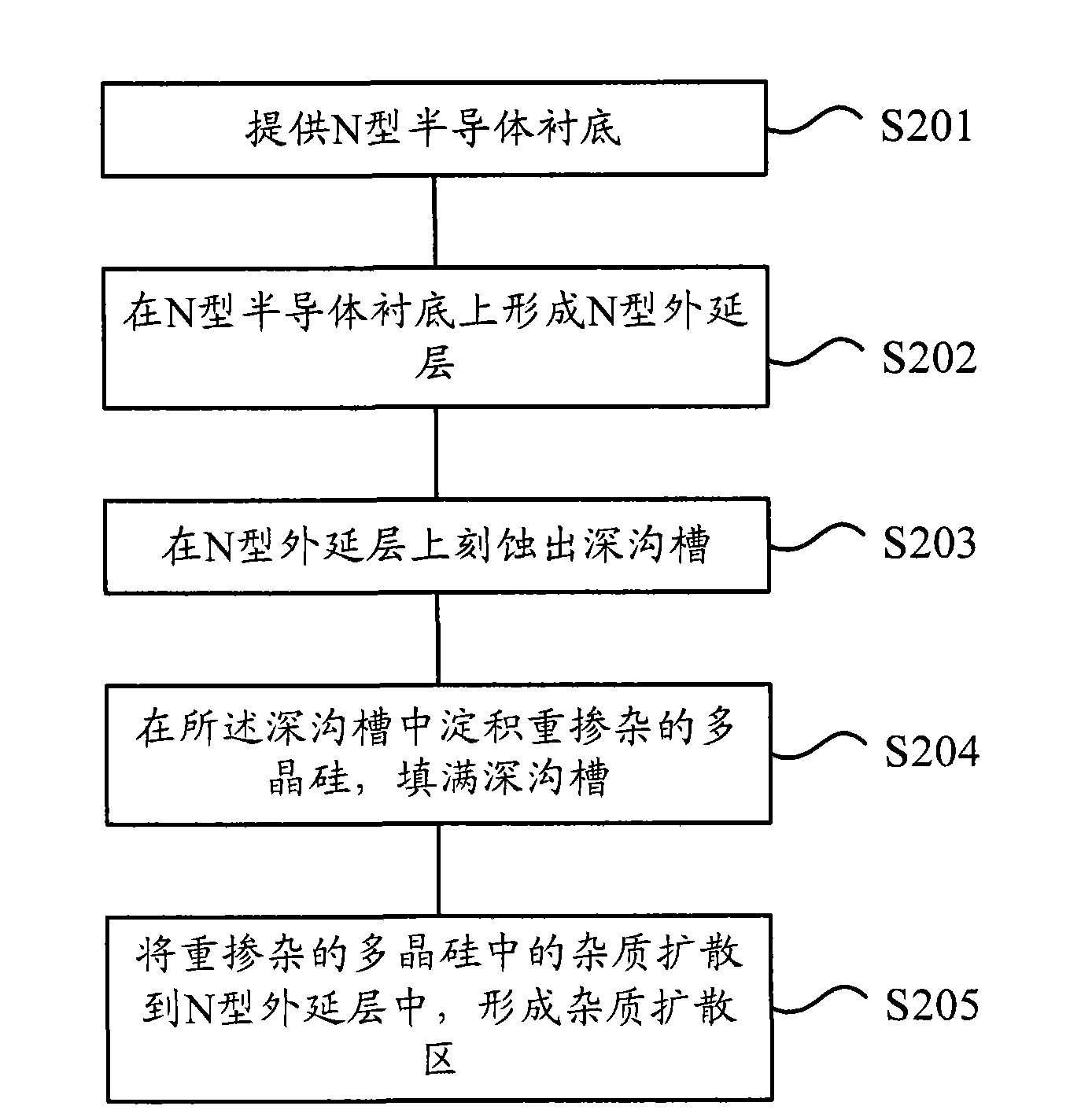

[0031] figure 2 It is a flowchart of a method for manufacturing a cold MOS super junction structure according to an embodiment of the present invention. As shown in the figure, the manufacturing method starts at step S201. The method may include: performing step S201, providing an N-type semiconductor substrate; performing step S202, forming an N-type epitaxial layer on the N-type semiconductor substrate; performing step S203, etching a deep trench on the N-type epitaxial layer; Step S204 is executed to deposit heavily doped polysilicon in the deep trench to fill up the deep trench; step S204 is executed to diffuse impurities in the heavily doped polysilicon into the N-type epitaxial layer to form an impurity diffusion region.

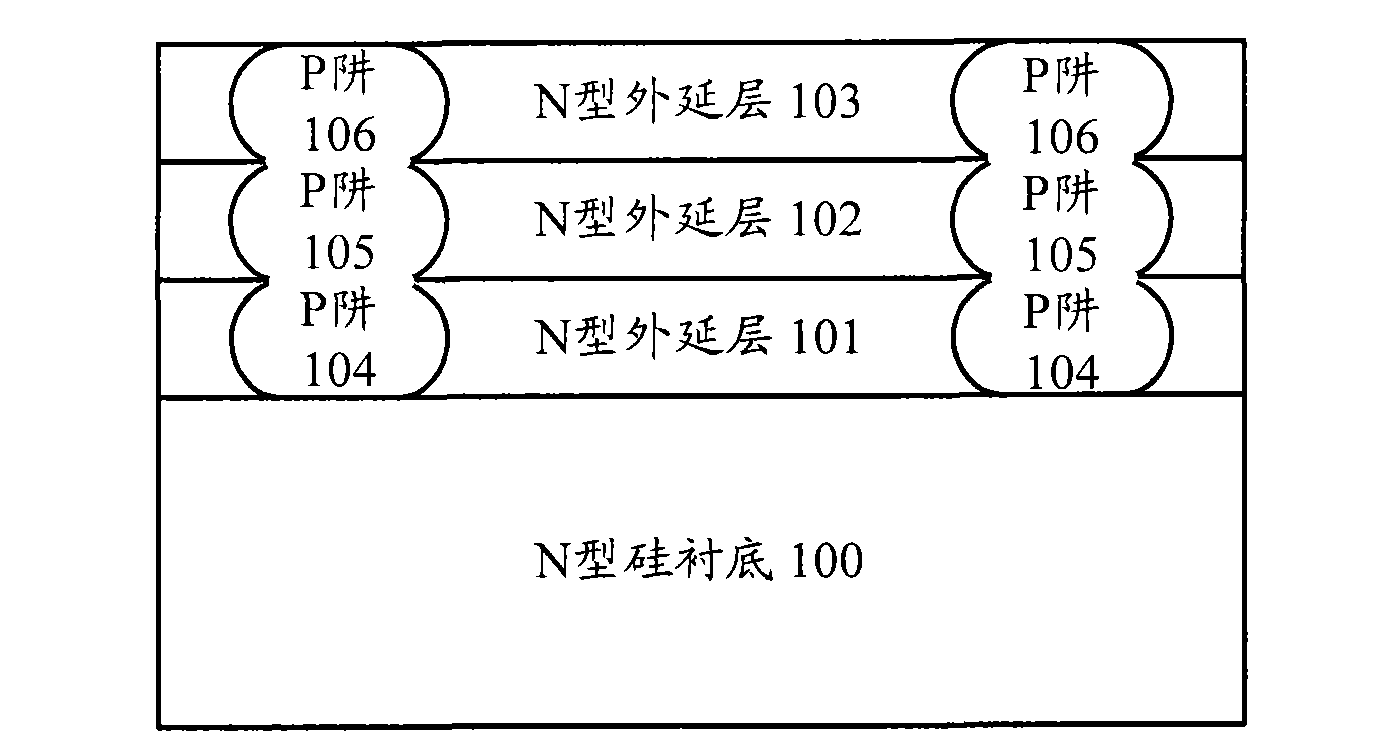

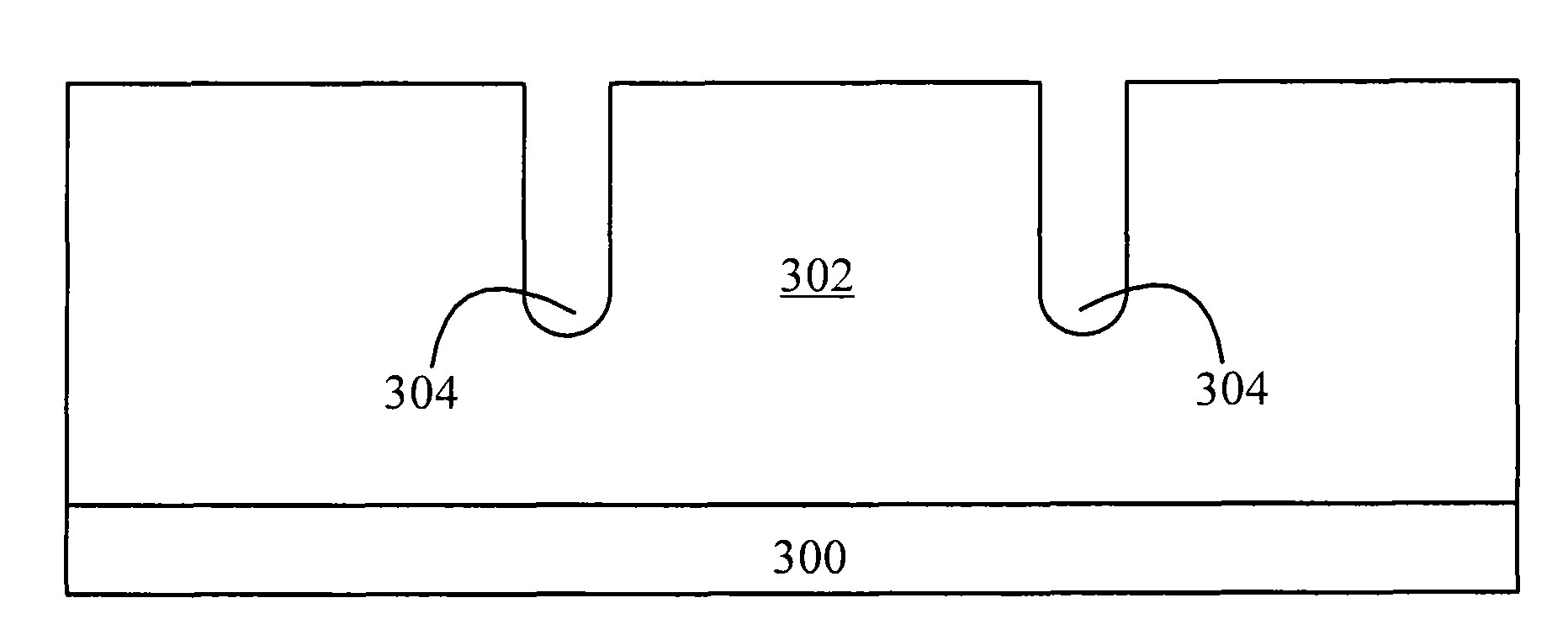

[0032] Figure 3 to Figure 5 It is a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More