Production method of shallow channel isolation region

A technique for shallow trench isolation and a manufacturing method, which is applied in the field of manufacturing shallow trench isolation regions, can solve problems such as etching residues, affecting isolation effects, and polysilicon residues, so as to reduce the formation of missing corners and avoid slow deposition rates. average effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

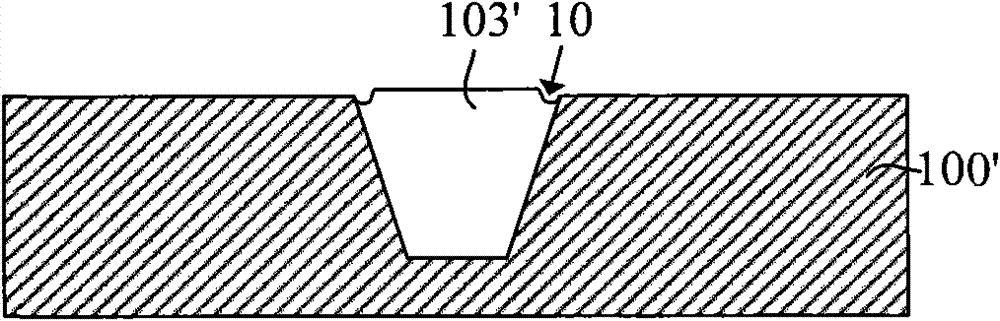

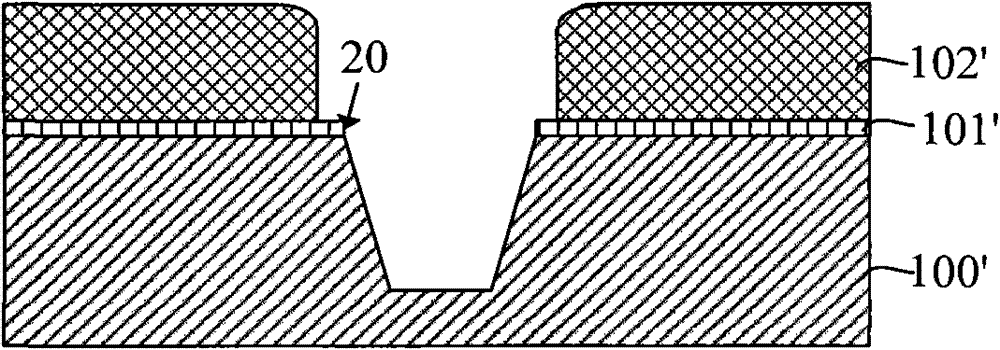

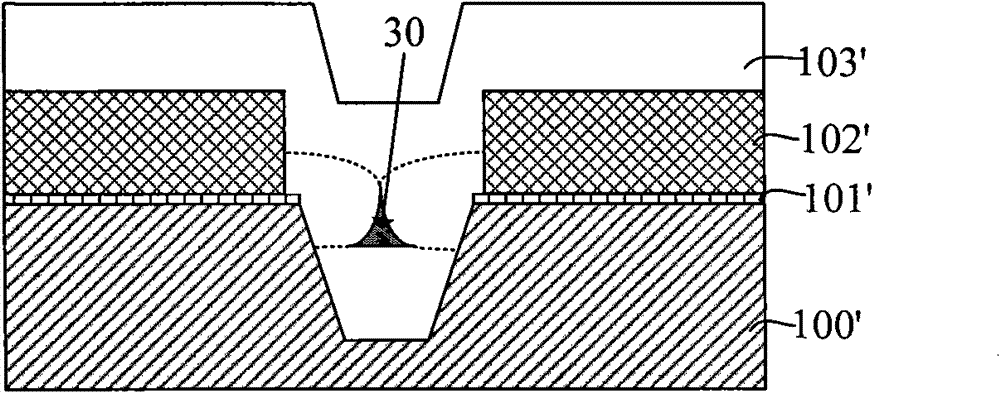

[0035] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be further described below in conjunction with the accompanying drawings. Of course, the present invention is not limited to this specific embodiment, what is the technology in this field? Common substitutions known to persons are also covered within the protection scope of the present invention.

[0036] Secondly, the present invention is described in detail by means of schematic diagrams. When describing the examples of the present invention in detail, for the convenience of explanation, the schematic diagrams are not partially enlarged according to the general scale, which should not be used as a limitation of the present invention.

[0037] The core idea of the present invention is: after the step of forming the oxide isolation layer, the mask layer is etched back, and an oxide layer is formed between the oxide isolation layer and the m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More