Thin film transistor and active matrix rear panel as well as manufacturing methods thereof and display

A technology of thin film transistor and manufacturing method, which is applied in the field of organic light emitting diode display, can solve the problems of low production yield, reduced yield, poor mobility uniformity, etc., and achieves the effects of performance advantages and simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

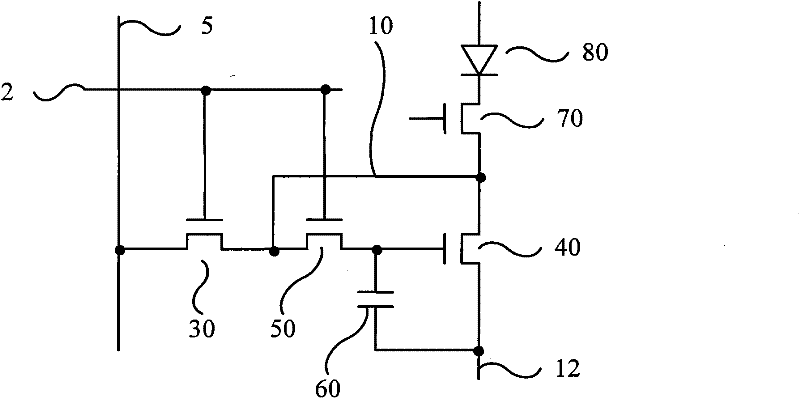

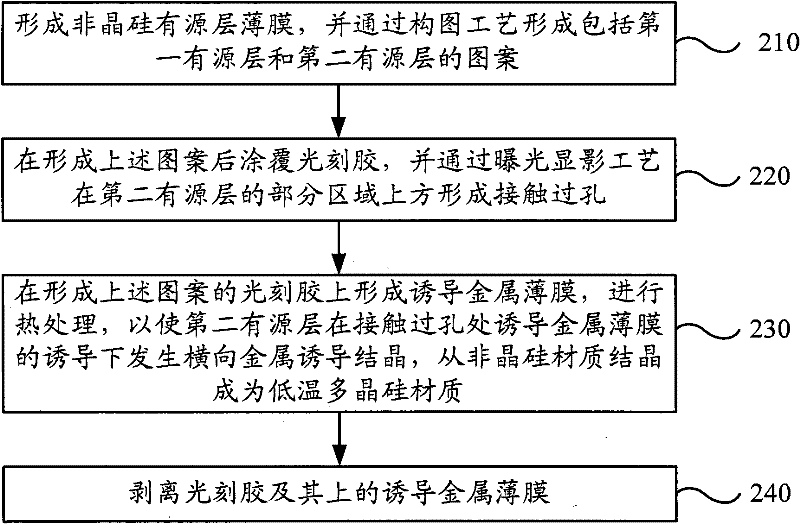

[0074] figure 2 The flow chart of the manufacturing method of the thin film transistor provided by Embodiment 1 of the present invention, the manufacturing method includes the process of preparing the first thin film transistor and the second thin film transistor, wherein the first thin film transistor and the second thin film transistor can be understood as two types Thin film transistors, the number of each type of thin film transistors may be one or more. The first thin film transistor includes a first gate electrode, a first active layer, a first drain electrode, and a first source electrode, and the second thin film transistor includes a second gate electrode, a second active layer, a second drain electrode, and a second source electrode. The structure of the electrode can be in the form of top gate or bottom gate. In the manufacturing method, the process of simultaneously preparing the first active layer and the second active layer specifically includes the following s...

Embodiment 2

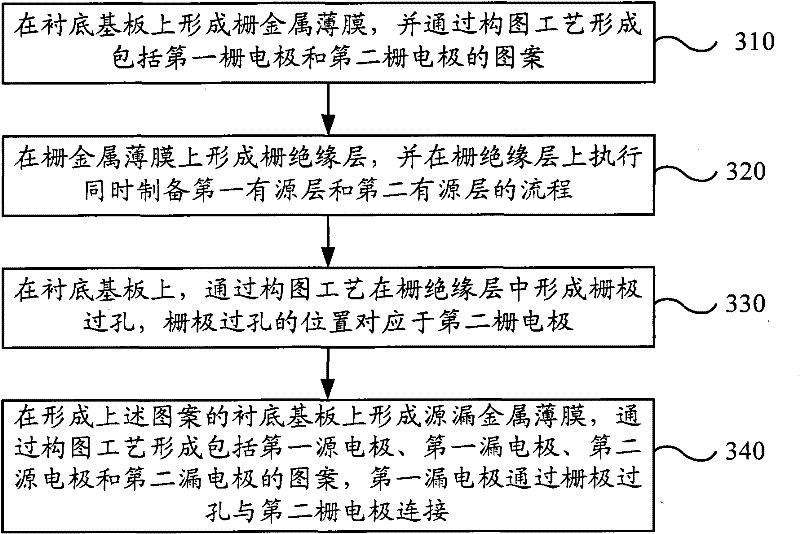

[0091] image 3 The flow chart of the manufacturing method of the thin film transistor provided by the second embodiment of the present invention, this embodiment can be based on the first embodiment, specifically a method for preparing a bottom-gate thin film transistor, then the first thin film transistor and the second thin film transistor are prepared The process of the transistor specifically includes the following steps:

[0092] Step 310, forming a gate metal thin film on the base substrate, and forming a pattern including a first gate electrode and a second gate electrode through a patterning process;

[0093] Step 320, forming a gate insulating layer on the substrate with the above-mentioned structure, and performing the process for simultaneously preparing the first active layer and the second active layer provided in Embodiment 1 on the gate insulating layer;

[0094] Step 330, forming a gate via hole in the gate insulating layer through a patterning process on the...

Embodiment 3

[0098] Figure 4 The flow chart of the manufacturing method of the thin film transistor provided by the third embodiment of the present invention, this embodiment can be based on the first embodiment, specifically a method for preparing a top-gate thin film transistor, then the first thin film transistor and the second thin film transistor are prepared The process of the transistor specifically includes the following steps:

[0099] Step 410, performing the process of simultaneously preparing the first active layer and the second active layer provided by Embodiment 1 on the base substrate;

[0100] Step 420, forming a gate insulating layer on the base substrate with the above pattern formed;

[0101] Step 430, forming a gate metal film on the gate insulating layer, and forming a pattern including the first gate electrode and the second gate electrode through a patterning process;

[0102] Step 440, forming a passivation layer on the base substrate on which the above pattern ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More