nldmos structure compatible with 5 volt cmos process and its fabrication method

A kind of process, N-type technology, applied in the field of NLDMOS structure and its manufacturing method, can solve the problems such as inability to share, and achieve the effect of a large safe working area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

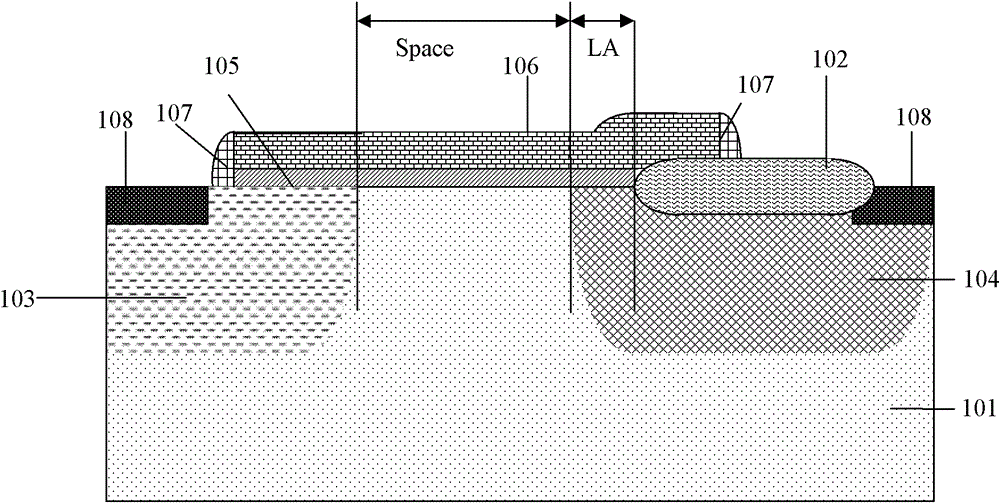

[0039] The NLDMOS structure compatible with the 5-volt CMOS process of the present invention, such as figure 1 As shown, it includes: a field oxygen region 102, a polysilicon gate 106, a gate oxide layer 105, an isolation spacer 107, and a source and drain 108 formed compatible with a 5-volt CMOS process, and a P-type notebook composed of a P well 103 in a CMOS process. The bottom region is an N-type drift region composed of an N well 104 in a CMOS process; wherein, the P-type background region and the N-type drift region are located in the P-type substrate 101, and the P-type background region and the N-type drift region The distance (Space) between them is 0.5-2 μm; the source and drain 108 are located in the P-type background region and the N-type drift region; the gate oxide layer 105 is located on the upper surface of the P-type substrate 101; the polysilicon gate 106 is located in the gate oxide layer 105; the isolation spacer 107 is adjacent to the polysilicon gate 106;...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More