Photoetching rework photoresist removing technology

A technology of photoresist and lithography, which is applied in the processing of photosensitive materials, electrical components, semiconductor/solid-state device manufacturing, etc., can solve the problems of wafer substrate unevenness and material, condition changes, unfavorable lithography, etc., to achieve The effect of stable secondary photolithography process, less raw material consumption, and improved stability and manufacturability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0028] Take polysilicon gate photolithographic rework at the 40nm technology node as an example.

[0029] As we all know, the lithography of the gate layer is one of the most important steps in the manufacturing process of integrated circuit chips, and the precision requirements are also the highest. In addition, the plasma in the ashing process will cause the loss of polysilicon and the distribution of ion-implanted impurities, so it is desirable to have a low-temperature and non-destructive adhesive removal method.

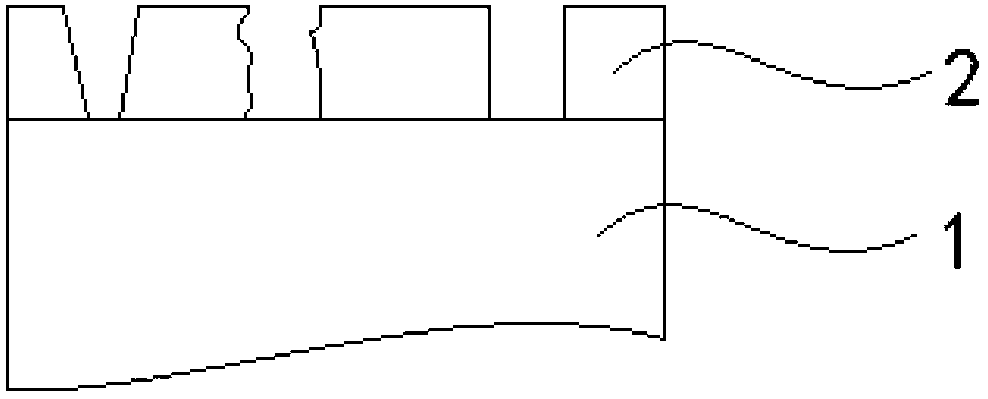

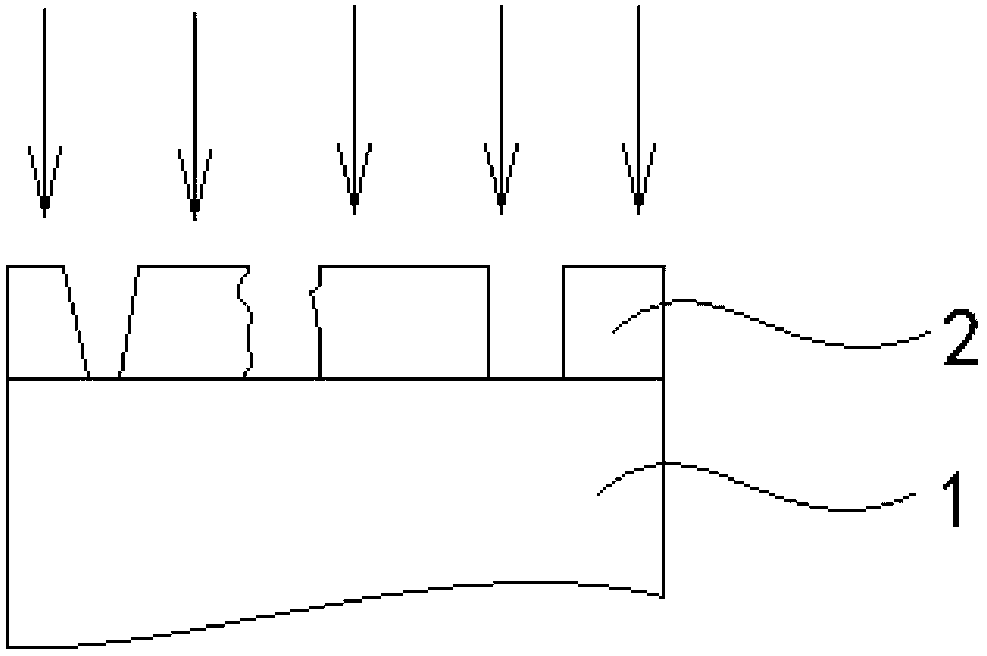

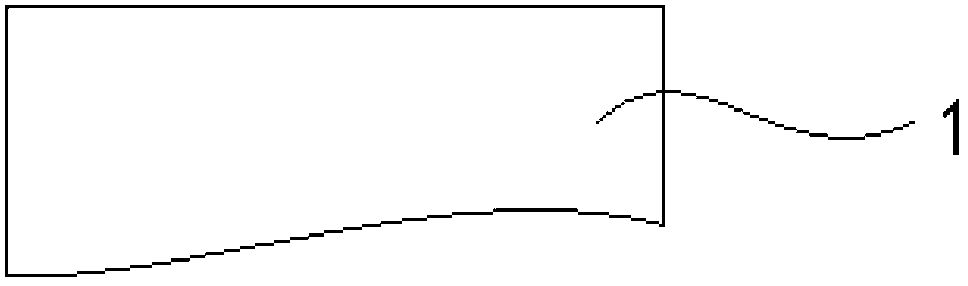

[0030] see Figure 1 to Figure 3 , the wafer process process completed the preparation of the polysilicon gate layer 1 at the 40nm node, and the polysilicon gate layer needs to be photoetched. After the first photoetching was performed using argon fluoride 193 nm ultraviolet light, a poor photoetching process occurred. Resulting in unacceptable size, registration and shape of the photoresist 2-hole slot, requiring photolithographic rework to remove all photores...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More