Fin field effect transistor and method of forming the same

A fin field effect and transistor technology, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve device performance problems and other problems, achieve stable performance, improve carrier mobility, and gate leakage current. small effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] As mentioned in the background, the performance of the prior art FinFETs is not stable.

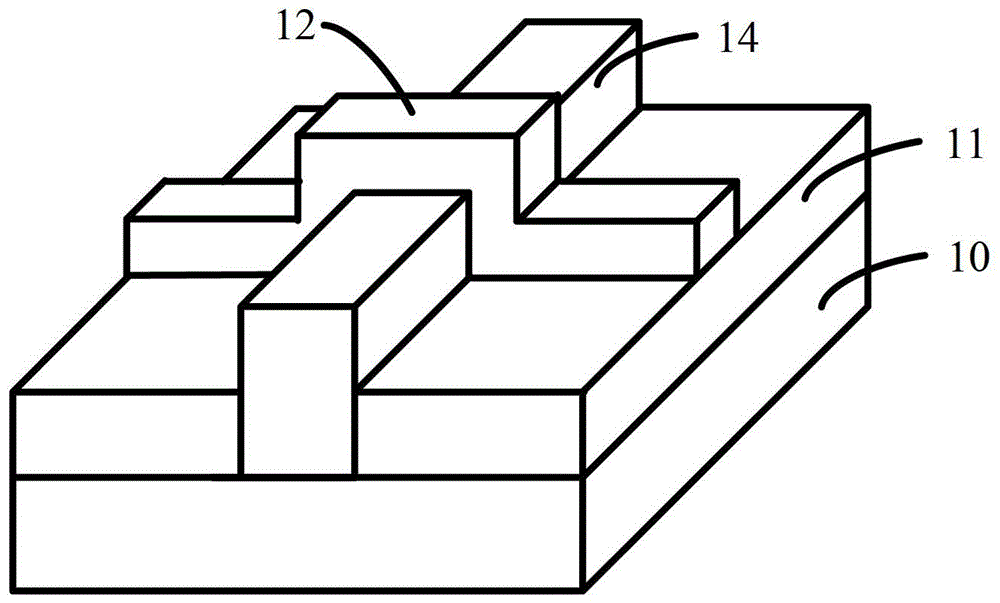

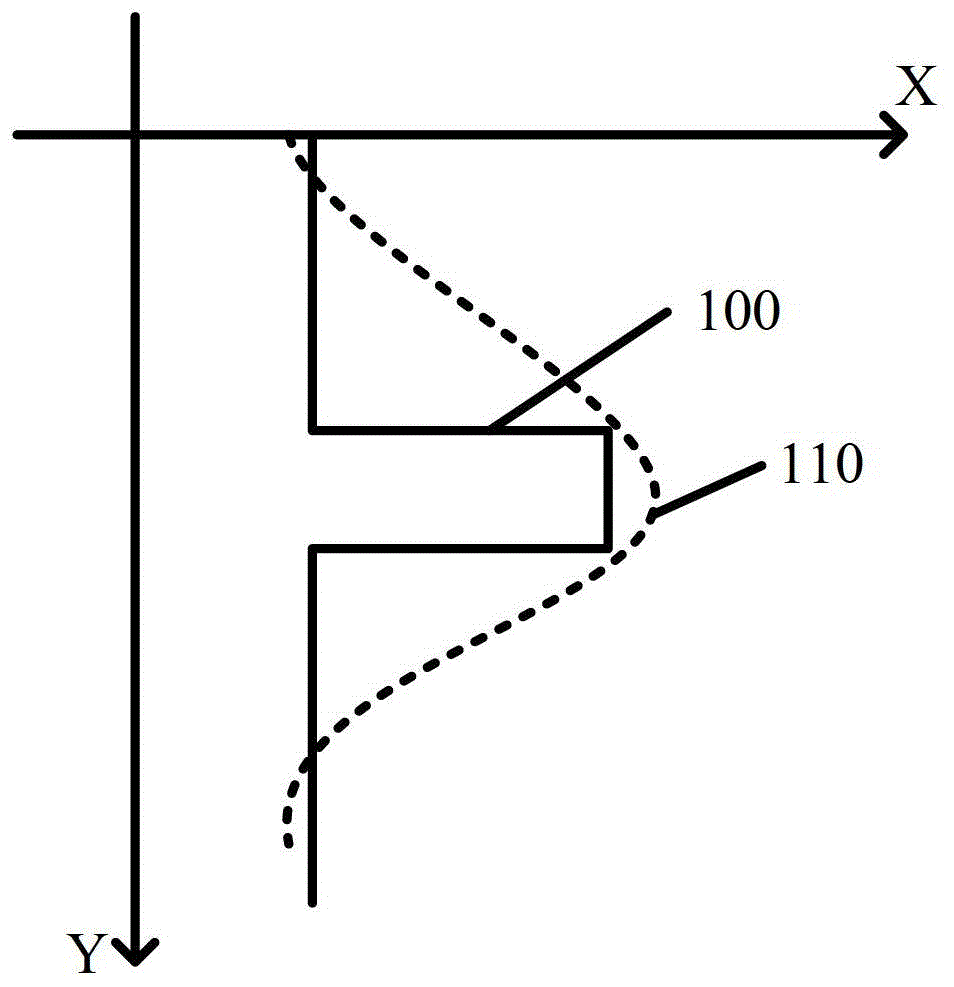

[0044] After research, it was found that after research, the inventor found that there are many reasons that affect the performance stability of the fin field effect transistor. One of the reasons is: the prior art forms fins 14 on the surface of the semiconductor substrate (such as figure 1As shown), doping ions from the top surface of the fin 14 to the inside of the fin 14 to improve the carrier mobility in the channel region of the fin field effect transistor, as figure 2 as shown in figure 2 The middle X-axis represents the concentration of dopant ions in the fin 14, and the Y-axis represents the distance from any point in the fin 14 to the top of the fin 14. In the case of ideal doping, it is desired that the ion concentration after doping be within the fin 14 As shown in the curve 100, the dopant ions are concentrated in the middle of the fin 14, while the ion concentratio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More