25Gbps data clock restoring circuit based on edge linearization technique

A data clock and recovery circuit technology, applied in the field of communications, can solve the problems of long locking time, poor jitter performance, and high requirements for phase detector logic circuits, and achieve the effect of reducing gain requirements, reducing speed requirements, and reducing design difficulty.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described below in conjunction with the drawings and embodiments.

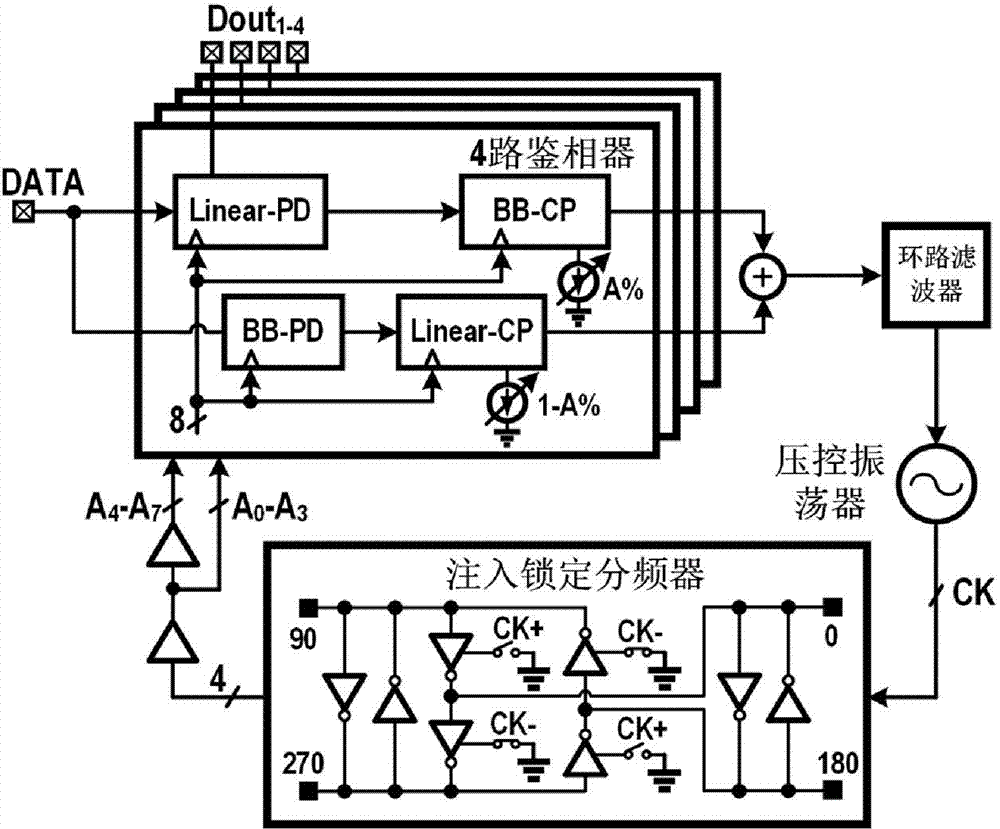

[0024] The structure of the circuit is as figure 1 As shown, a differential sine clock (CK) generated by a voltage-controlled oscillator (VCO) working at 12.5GHz. The two sine clocks are injected into the ring oscillator-based injection latch divider for frequency division by two to produce a 4-phase 6.25 GHz differential quadrature clock (A0-A3). The A0-A3 differential quadrature clock passes through the variable delay unit to generate a 4-phase differential quadrature clock (A4-A7), and forms an 8-phase 6.25GHz clock with the previous 4-phase. The 8-phase clock passes through 8 buffers to enhance its driving ability, so as to oversample the input 25Gbps differential data DATA at 2 times the rate.

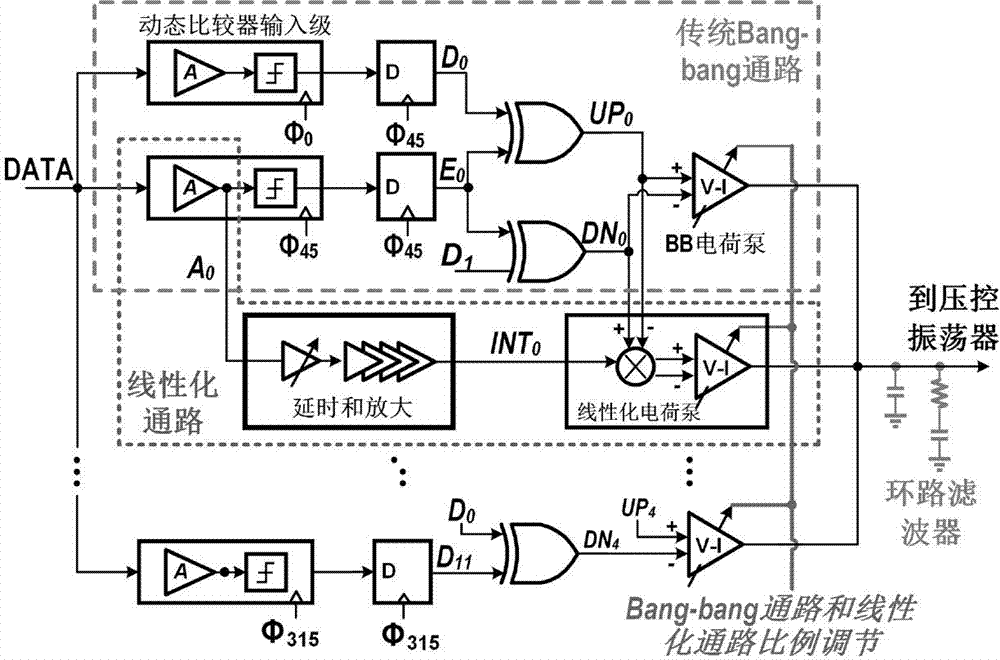

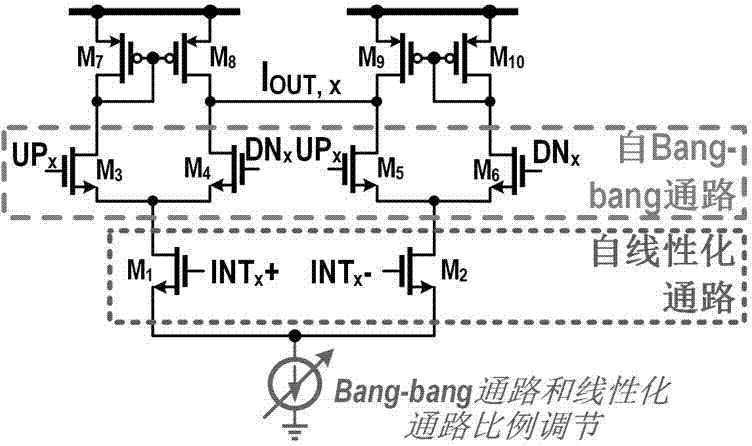

[0025] In order to reduce the requirements for dynamic comparators, flip-flops and logic circuits, the phase detector adopts a 4-way parallel structure. In every way ( fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More