On-chip array thermoelectric converter of field effect transistor and fully-automatic alignment manufacturing technology thereof

A field effect transistor and manufacturing process technology, which is applied to the field effect transistor on-chip array thermoelectric converter and its fully self-aligned manufacturing process field, can solve the problems of insufficient overload capacity, poor dynamic characteristics, slow response speed, etc., and achieves dynamic characteristics and Excellent overload characteristics, fast response speed, and the effect of measuring frequency bandwidth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

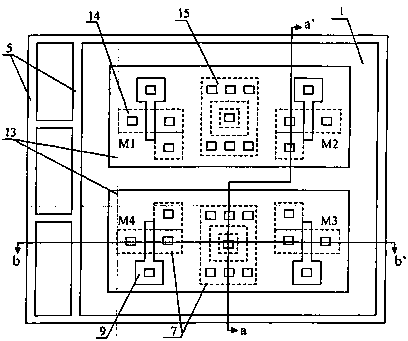

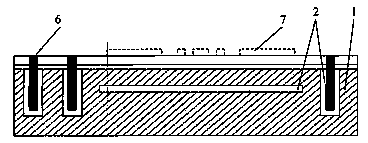

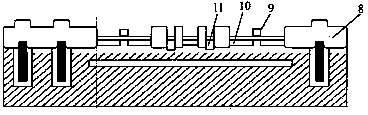

[0038] A field effect tube chip array thermoelectric converter, such as figure 1 , Figure 2A , Figure 2B , Figure 2C , Figure 3A , Figure 3B As shown, it includes a P-type silicon substrate 1, a silicon island 13, a boron-doped silicon layer 2, a deep groove 5, polysilicon 6, a field oxide layer 8, and an etched groove 12. The P-type silicon substrate 1 is processed There are two silicon islands 13, and the P-type silicon substrate 1 is implanted with a boron-doped silicon layer 2 corresponding to the bottom of the area of the silicon island 13. The P-type silicon substrate 1 is processed with square deep grooves 5 around the edge, and the left deep groove 5 A deep groove 5 parallel to it is processed beside it, and a rich boron-doped silicon layer 2 is injected into the deep groove 5, and the polysilicon 6 is filled in the deep groove 5, and the deep boron-doped silicon layer 2 is filled, and the deep groove 5 and the silicon island 13, The two silicon islands 13 ...

Embodiment 2

[0062] A field effect tube chip array thermoelectric converter, such as figure 1 , Figure 2A , Figure 2B , Figure 2C , Figure 3A , Figure 3B As shown, it includes a P-type silicon substrate 1, a silicon island 13, a boron-doped silicon layer 2, a deep groove 5, polysilicon 6, a field oxide layer 8, and an etched groove 12. The P-type silicon substrate 1 is processed There are two silicon islands 13, and the P-type silicon substrate 1 is implanted with a boron-doped silicon layer 2 corresponding to the bottom of the area of the silicon island 13. The P-type silicon substrate 1 is processed with square deep grooves 5 around the edge, and the left deep groove 5 A deep groove 5 parallel to it is processed beside it, and a rich boron-doped silicon layer 2 is injected into the deep groove 5, and the polysilicon 6 is filled in the deep groove 5, and the deep boron-doped silicon layer 2 is filled, and the deep groove 5 and the silicon island 13, The two silicon islands 13 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More