Forming method of conductive plug

A technology of conductive plugs and conductive materials, applied in the direction of circuits, electrical components, electrical solid devices, etc., can solve the problems of easy collapse, poor etch resistance, low yield, etc., and achieve good appearance, high etch resistance, The effect of high yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

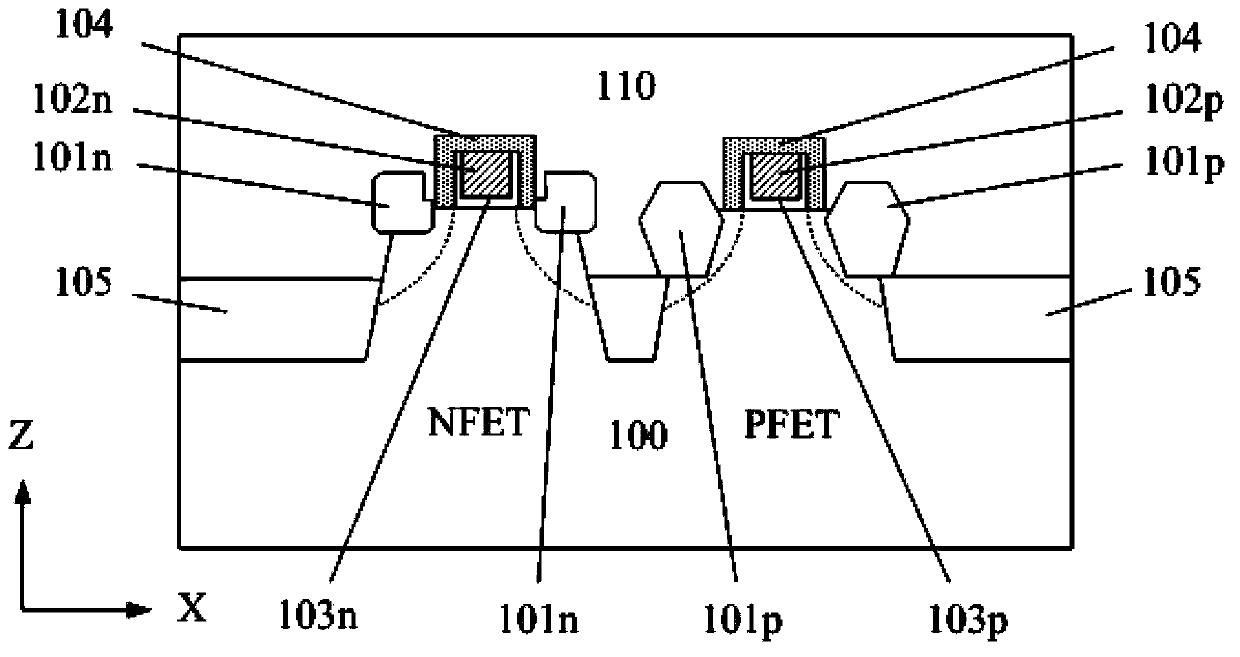

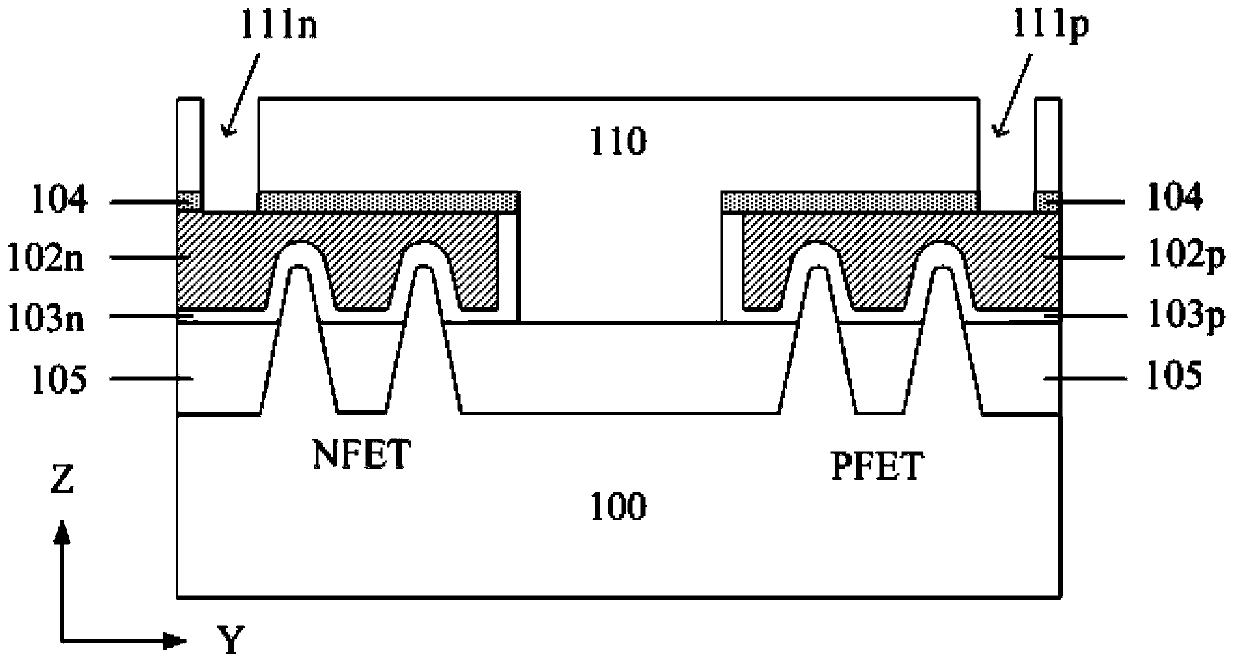

[0040] It can be known from the background art that in the conventional method for forming a conductive plug, a relatively thick low temperature oxide layer needs to be used as a mask. However, the use of a thicker low temperature oxide layer tends to result in a low yield of formed conductive plugs.

[0041] Taking the fin field effect transistor in the prior art as an example, the distance between the source region and the drain region on the same fin field effect transistor is getting smaller and smaller, although the gate region contact holes can be arranged on the gates on both sides of the fin part. Therefore, the distance between the contact holes in the gate region is relatively large, that is, the contact holes in the gate region can use a low temperature oxide layer as a mask. However, when the low temperature oxide layer is used as a mask to form the source contact holes and the drain contact holes, it is easy to cause the low temperature oxide layer to collapse, so...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More