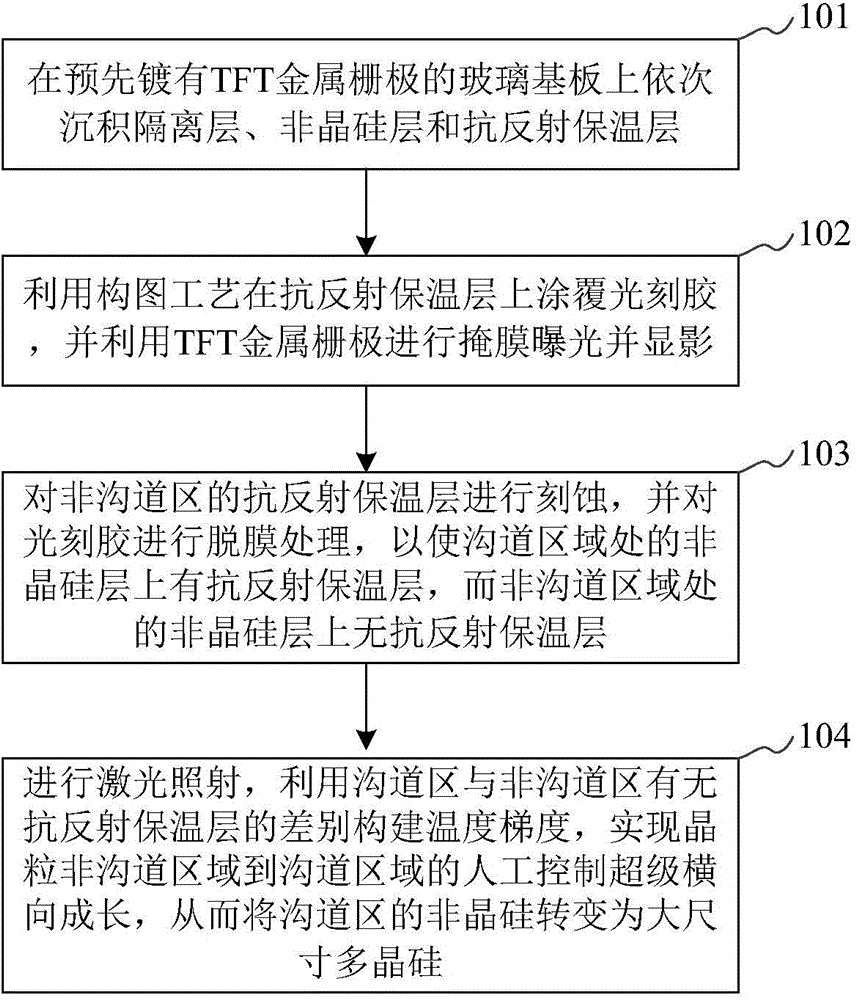

Thin film transistor low-temperature polycrystalline silicon thin film manufacturing method

A thin-film transistor and low-temperature polysilicon technology, which is applied in the manufacture of transistors, semiconductor/solid-state devices, semiconductor devices, etc., can solve the problems of increasing the production cost of flat-panel displays, different numbers of grain boundaries, and uneven device performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0042] see figure 1 , Figure 2(A) to Figure 2(C) , In one embodiment, a method for preparing a low-temperature polysilicon thin film for a thin film transistor is provided. The method is applied in the preparation process of a thin film transistor with an inverted gate structure, and the method includes:

[0043] Step 101 , depositing an isolation layer, an amorphous silicon layer and an anti-reflection insulation layer in sequence on the glass substrate pre-plated with a TFT metal gate.

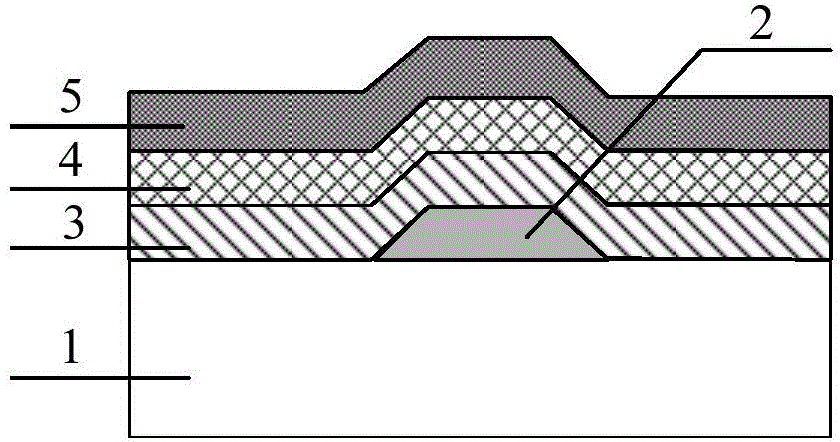

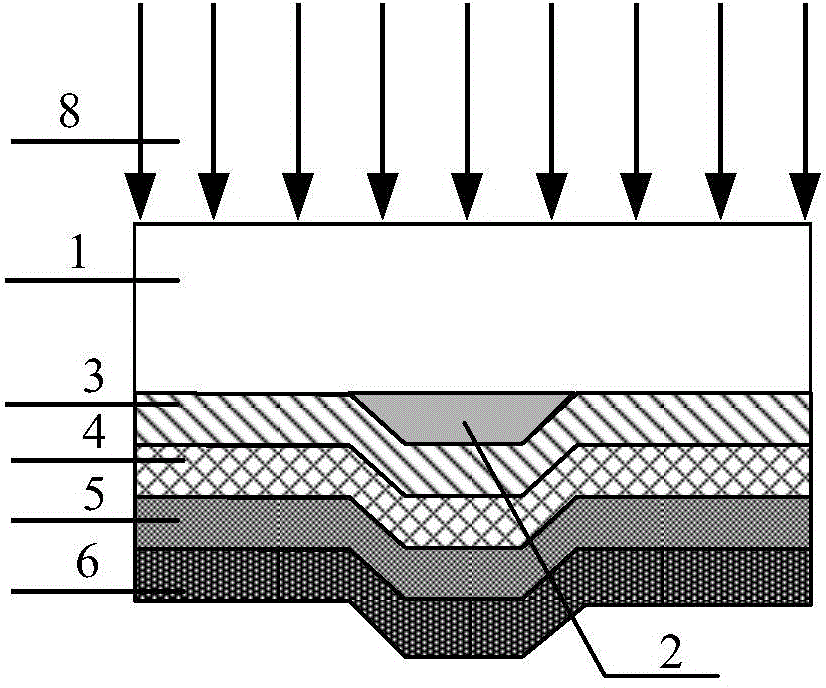

[0044] Specifically, as shown in FIG. 2(A), during the preparation process of the thin film transistor wit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More