Wafer-level fan-out PoP encapsulation structure and making method thereof

A packaging structure, wafer-level technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

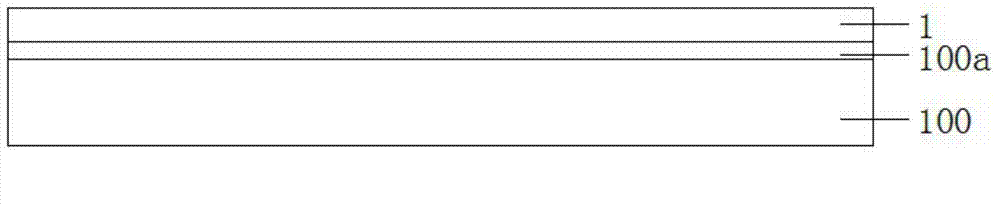

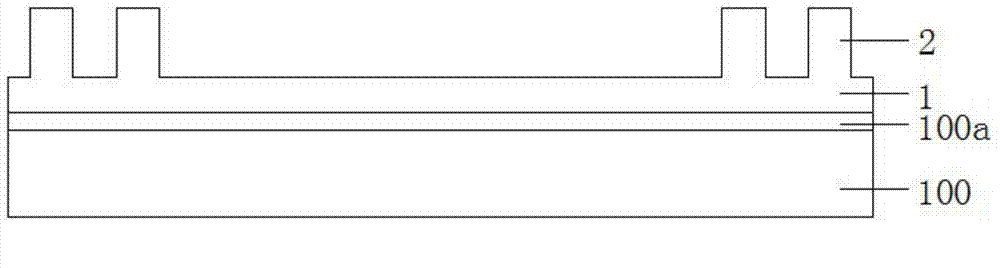

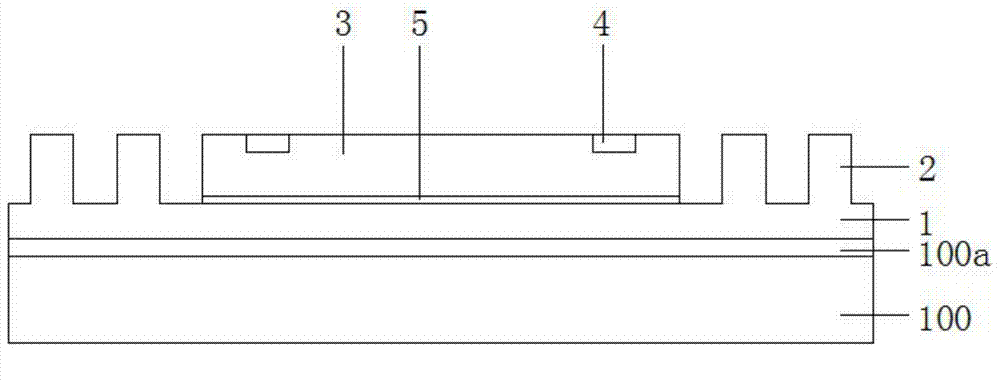

[0045]In order to make the purpose, technical solution and advantages of the present invention clearer, the specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings.

[0046] Such as Figure 14 As shown, a wafer-level fan-out PoP packaging structure is formed by stacking at least one fan-out PoP packaging unit; a fan-out PoP packaging unit is composed of two packages with the same structure;

[0047] The one package includes a metal bump structure 2, an IC chip 3, a bonding pad 4, a second paste material 5, a first plastic packaging material 6, a first rewiring metal wiring layer 7, and a first metal layer 8 , the first dielectric material layer 9, the second rewiring metal wiring layer 10, the second dielectric material layer 11, the second metal layer 12; the IC chip 3 has a bonding pad 4, and the second paste material 5 is pasted on the surface of the IC chip 3, the first plastic encaps...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More