Wafer positioning method

A positioning method and wafer technology, applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of difficult positioning of wafers, avoid low yield, reduce resistance value, and ensure the reliability of subsequent devices The effect formed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be noted that all the drawings of the present invention are in simplified form and use inaccurate scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

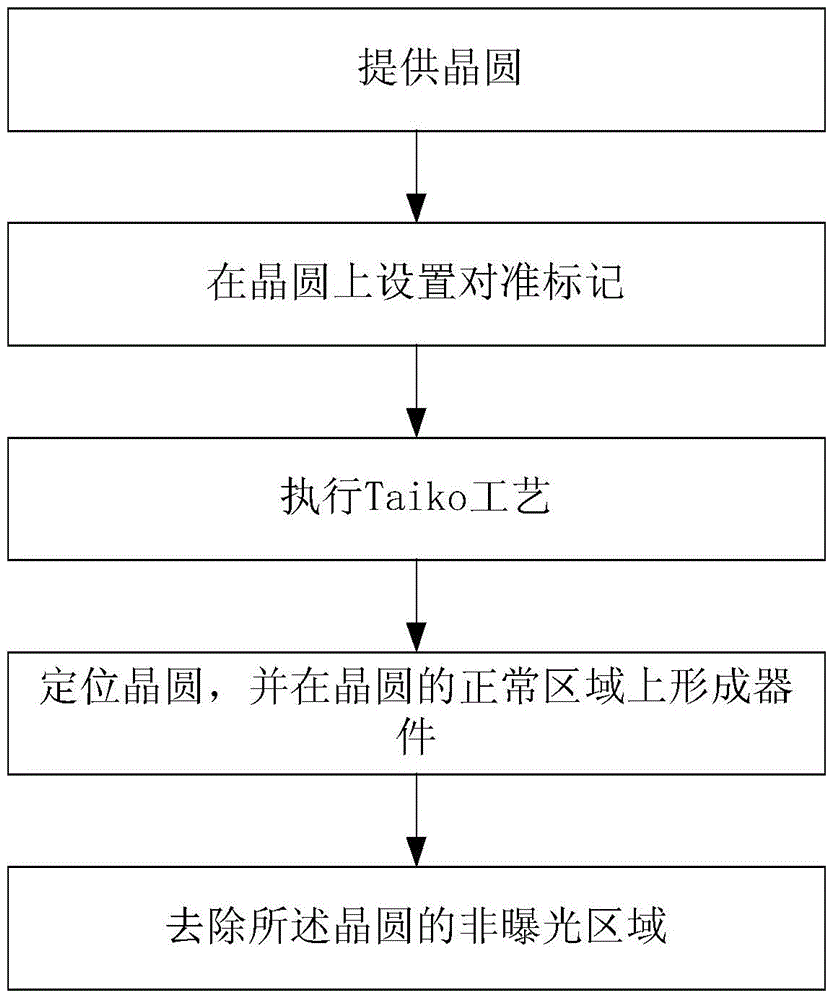

[0019] Such as figure 1 As shown, the present invention provides a wafer positioning method, specifically comprising the following steps:

[0020] Step 1: Provide a wafer, which includes a normal area and a non-exposed area. Wherein, the normal area of the wafer is an area for subsequent exposure and device formation; the non-exposed area is an edge portion of the wafer, which is set around the normal area and does not need to form devices thereon. In the present invention, after the device is forme...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More