A kind of lateral diffusion semiconductor device and its preparation method

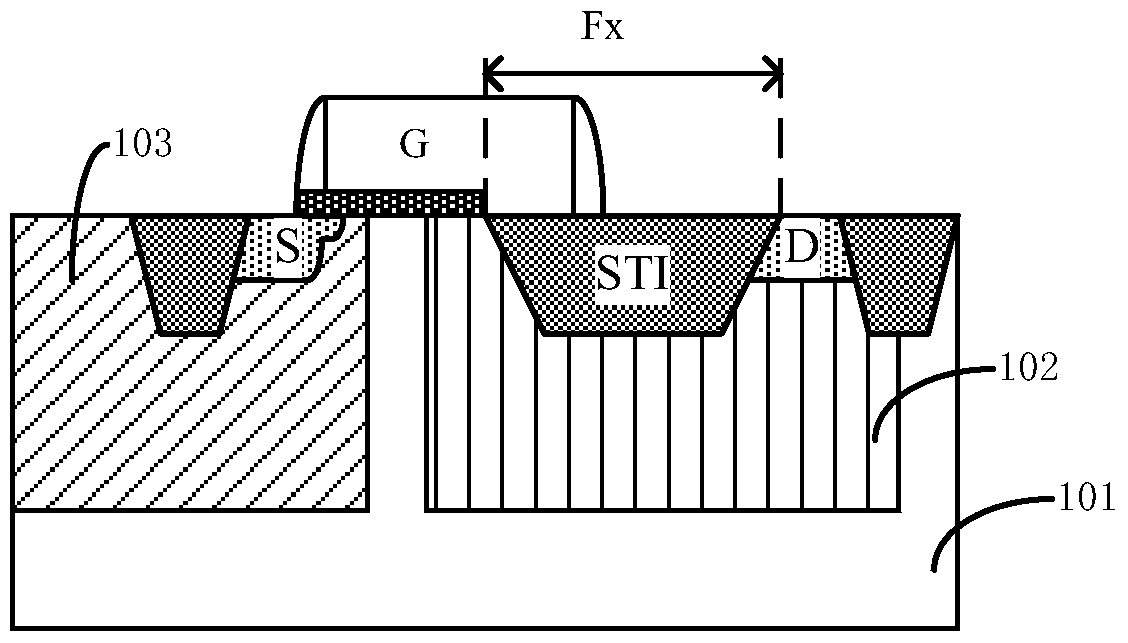

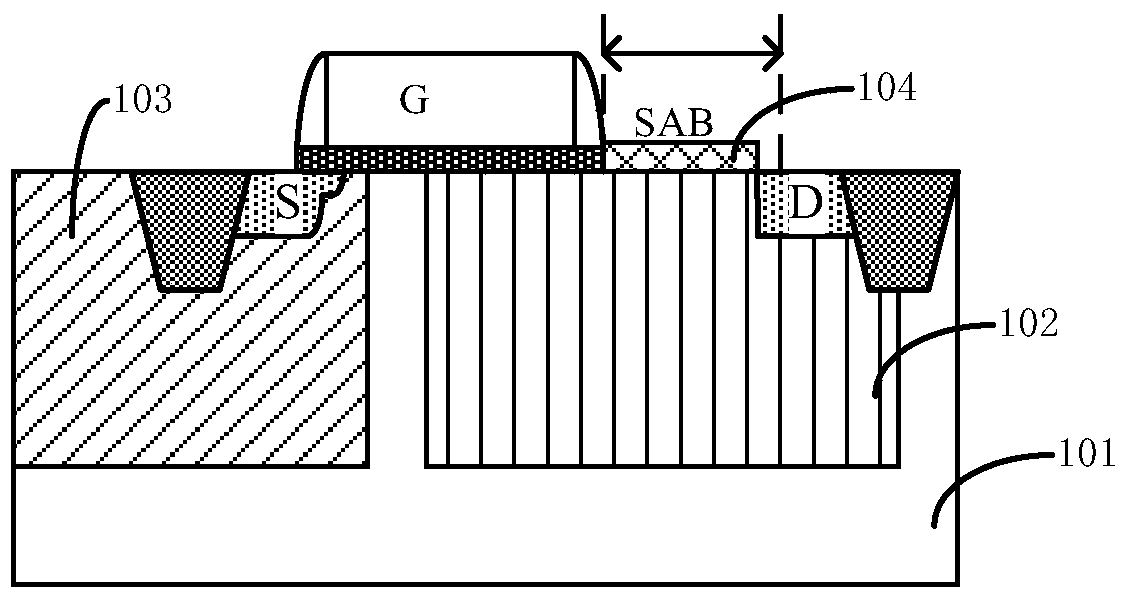

A semiconductor and device technology, applied in the field of lateral diffusion semiconductor devices and their preparation, can solve the problems of limiting the switching speed of LDMOS, the influence of device breakdown voltage, increasing parasitic capacitance, etc., to improve the breakdown voltage BV, reduce Rdson, reduce Effect of on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0048] The invention provides a method for preparing a laterally diffused semiconductor device, comprising: providing a semiconductor substrate, in which a laterally isolated body region and a drift region are formed, and mutually isolated A gate structure and a dummy gate structure, wherein the gate structure is partly located on the body region, partly located on the drift region, and the dummy gate structure is located on the drift region;

[0049] performing a source-drain implantation step to form a source region in the body region on one side of the gate structure, and to form a drain region in the drift region on the side of the dummy gate structure away from the source region;

[0050] A source metal layer and a drain metal layer are respectively formed above the source region and the drain region to form an electrical connection, wherein the source metal layer extends toward the drain region to form a field plate structure, and the drain region Adjusting the electric ...

Embodiment 1

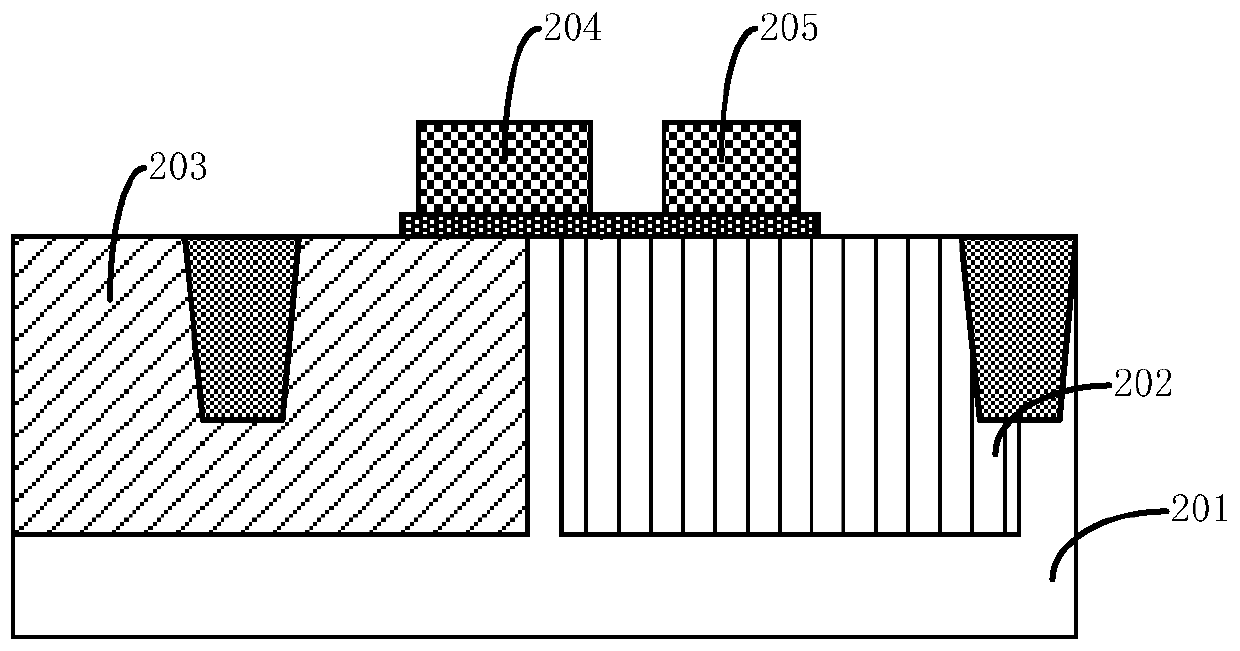

[0052] Attached below Figure 2a-2d The preparation method of the LDMOS of the present invention is further described.

[0053] First, step 201 is performed to provide a semiconductor substrate 201 in which a body region 203 and a drift region 202 are formed.

[0054] Specifically, refer to Figure 2a , wherein the semiconductor substrate 201 can be silicon, silicon-on-insulator (SOI), silicon-on-insulator (SSOI), silicon-germanium-on-insulator (S-SiGeOI), silicon-germanium-on-insulator (SiGeOI) and germanium-on-insulator (GeOI), etc.

[0055] A body region 203 is formed in the semiconductor substrate 201, which has a first conductivity type. In a specific embodiment of the present invention, the body region 203 is N+ or P+ doped, for example, an N-type dopant ( For example, phosphorus) is implanted into the semiconductor substrate, and the dopant is driven in by a heat treatment process, thereby forming the N-type well region.

[0056] Before performing ion implantation t...

Embodiment 2

[0093] The present invention also provides a laterally diffused semiconductor device, such as Figure 2d shown, including:

[0094] semiconductor substrate 201;

[0095] a body region 203 and a drift region 202 located in the semiconductor substrate 201;

[0096] A gate structure 204 and a dummy gate structure 205, there is a gap between the gate structure 204 and the dummy gate structure 205, wherein the gate structure 204 is partly located on the body region 203 and partly located in the drift region 202, the dummy gate structure 205 is located on the drift region 202;

[0097] a source region and a drain region, the source region is located in the body region 203 on the side of the gate structure 204, and the drain region is located in the drift of the dummy gate structure 205 on the side away from the source region District 202;

[0098] The source metal layer 210 and the drain metal layer 208 are electrically connected to the source region and the drain region respect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More