III-V clan nano wire planar transistor based on SOI substrate and preparation method thereof

A nanowire and transistor technology, applied in the field of III-V nanowire planar transistors and their preparation, can solve problems such as unfavorable preparation, and achieve the effects of eliminating rectification effect, facilitating integration, and simple device preparation process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

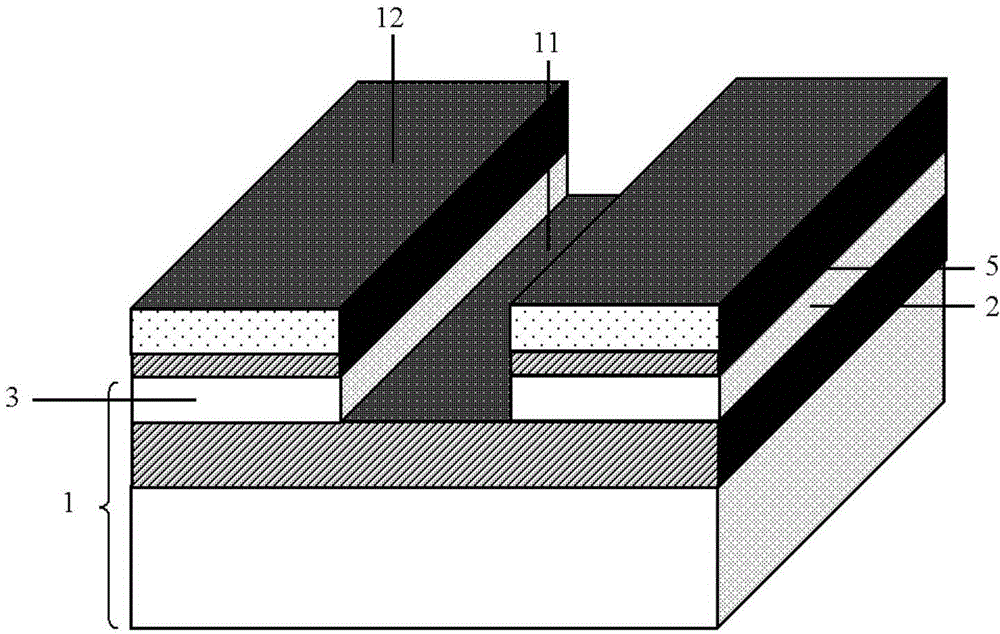

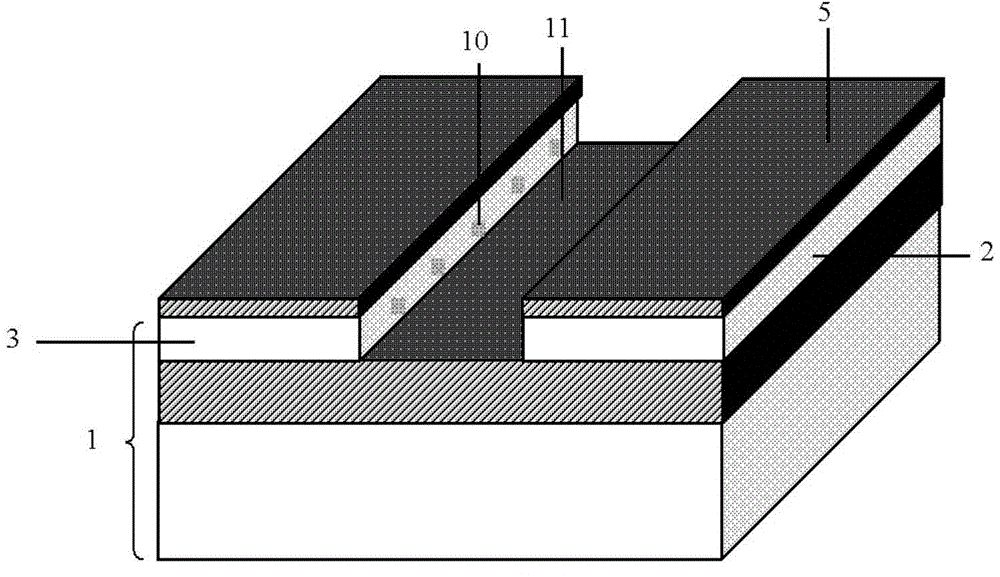

[0039] see Figure 1-Figure 5 As shown, the present invention provides a kind of III-V family nanowire planar transistor based on SOI substrate, comprising:

[0040] An SOI substrate 1, wherein the top layer silicon of the SOI substrate 1 is a (110) crystal plane, and the thickness is 88nm;

[0041] A source region 2 and a drain region 3, the source region 2 and the drain region 3 are formed on the SOI substrate 1, wherein the silicon crystal planes of the side walls of the source region 2 and the drain region 3 are {111} crystal planes, and the doping type It is N-type with a doping concentration of 10 18 -10 19 cm -3 , the ion implantation junction depth is 17-100nm;

[0042] A plurality of III-V group nanowires 4, the plurality of III-V group nanowires 4 connect the source region 2 and the drain region 3 to form a conductive channel, wherein the plurality of III-V group nanowires 4 can be In x Ga 1-x As(0≤x≤1), GaP, GaN or InP materials, the high electron mobility of ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More