Test structure and test method

A technology of test structure and test method, which is applied in the direction of semiconductor/solid-state device test/measurement, single semiconductor device test, electrical components, etc. Problems such as failure location to achieve good test results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

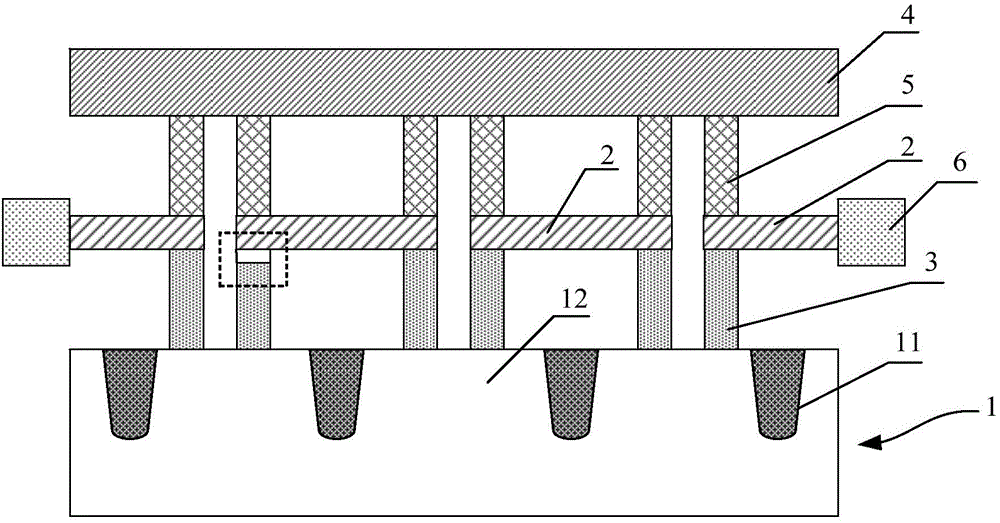

[0038] see image 3 , the present invention provides a test structure, the test structure can be designed on the wafer dicing road, including a substrate layer 1 and a number of discrete first interlayer metal layers 2, the first interlayer metal layer 2 and the The substrate layers 1 are electrically connected through a number of first contact plugs 3; the test structure also includes a second interlayer metal layer 4 distributed continuously, and the second interlayer metal layer 4 is connected through a number of second contact plugs. It is electrically connected with the first interlayer metal layer 2 described in 5 .

[0039] Specifically, the substrate layer 1 may be a device layer or a metal interconnection layer. That is, the test structure of the present invention can be used to monitor the contact condition between the contact layer (CT layer) and the first metal layer (metal-1) on the device layer, and can also be used to monitor a certain via layer ( Via layer) a...

Embodiment 2

[0046] The present invention also provides a test method for testing the top contact of a contact plug using the test structure in Embodiment 1, which at least includes the following steps: firstly remove the substrate layer 1 from the back of the test structure to expose the first contact plugs 3, and then observe the lightness and darkness of the first contact plugs under a scanning electron microscope, if one of the first contact plugs is darker than the other first contact plugs, then it is judged that the first contact plug is different from the other first contact plugs. The disconnected connection between the first interlayer metal layers.

[0047] see Figure 4 , is shown as a cross-sectional view of the test structure after the substrate layer has been removed. At this time, observing the lightness and darkness of the first contact plug 3 under a scanning electron microscope can locate the disconnected connection position.

[0048] Specifically, the substrate layer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More