Formation method of semiconductor structure

A semiconductor and graphics technology, applied in the direction of semiconductor devices, etc., can solve the problem that the electrical performance of the semiconductor structure needs to be improved, and achieve the effect of avoiding channel length changes, good consistency, and small line width roughness.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

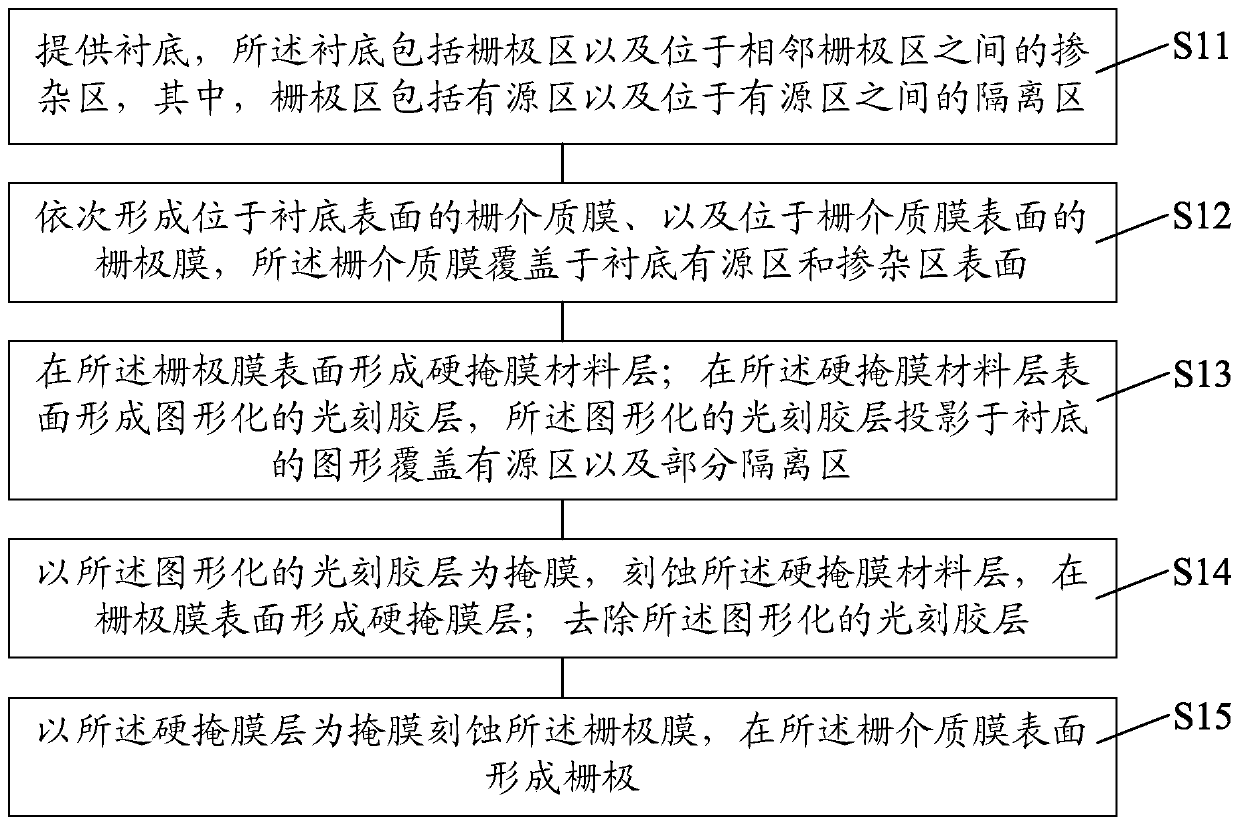

[0032] It can be seen from the background art that the electrical performance of the semiconductor structure formed in the prior art needs to be improved.

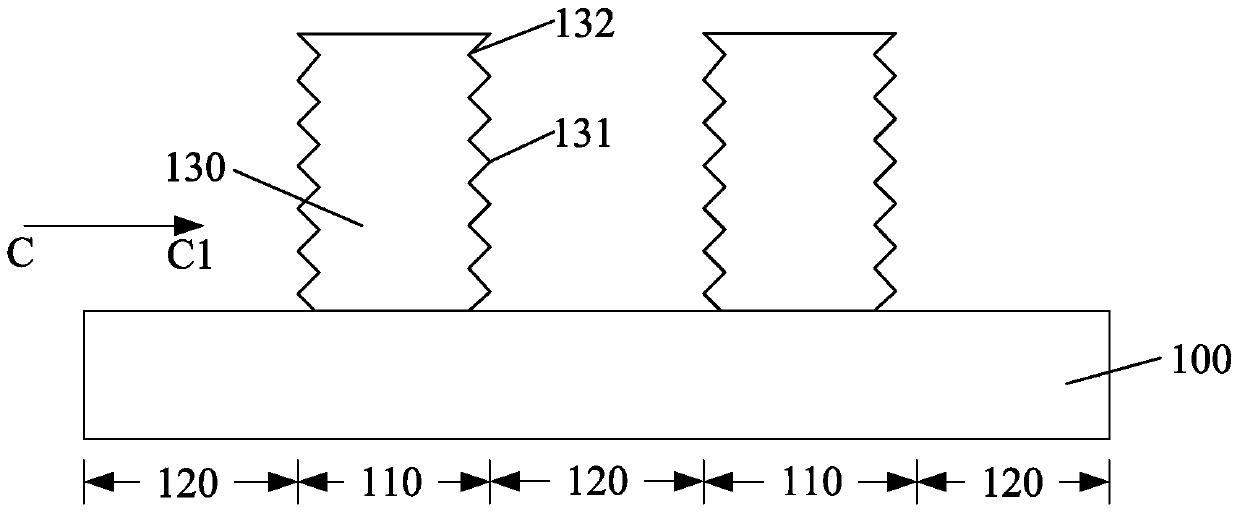

[0033] Such as figure 2 as shown, figure 2 A cross-sectional schematic diagram of a semiconductor structure formed by a method provided in the prior art, including: a substrate 100, the substrate 100 including a gate region 110 and a doped region 120 adjacent to the gate region 110, the gate region 110 includes an active region and an isolation region adjacent to the active region, and the width dimension of the gate region 110 (that is, the distance from the source region to the drain region), the width dimension of the active region and the isolation region are consistent, and the formed gate The pole 130 covers the active area and part of the isolation area. Ideally, the width dimension of the patterned photoresist layer is consistent with the width dimension of the active region, so that the length of the formed ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More