Semiconductor device with superjunction structure and preparation method thereof

A semiconductor and device technology, which is applied in the field of semiconductor devices with super junction structure and its preparation, can solve the problems of increased switching loss of semiconductor devices, reduced durability of semiconductor devices, and high breakdown voltage of cell regions, so as to reduce the switching Loss, reduce loss and voltage oscillation, optimize the effect of breakdown position

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

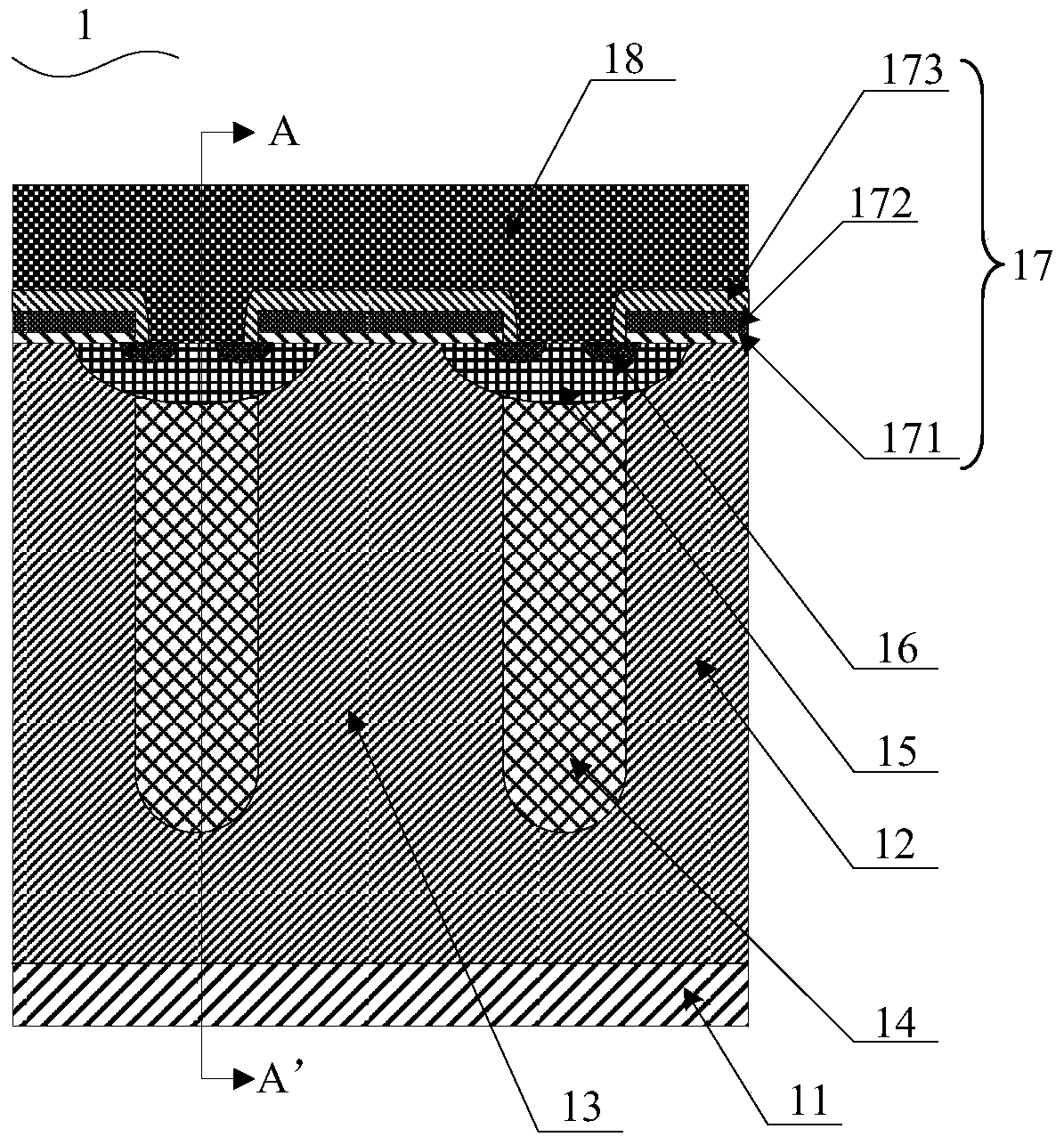

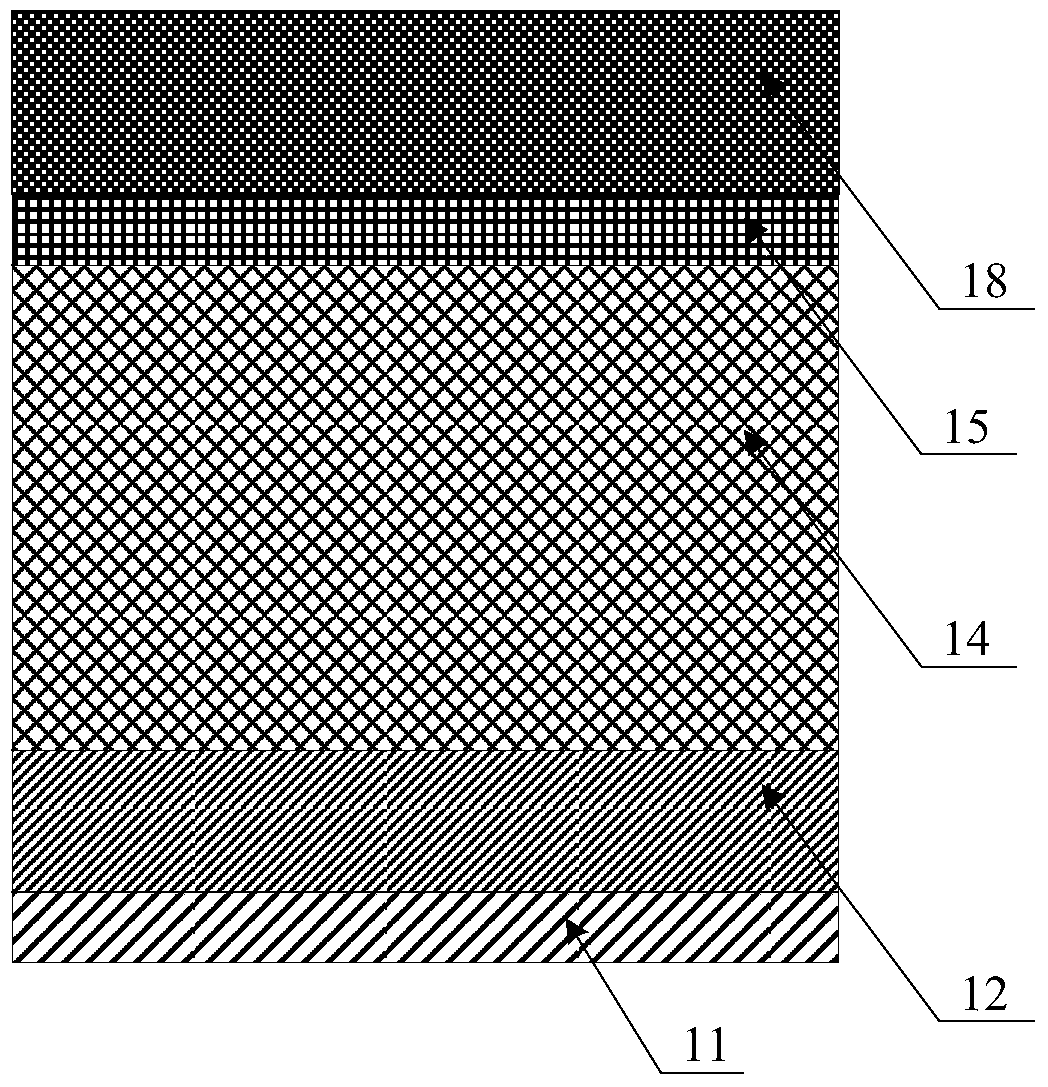

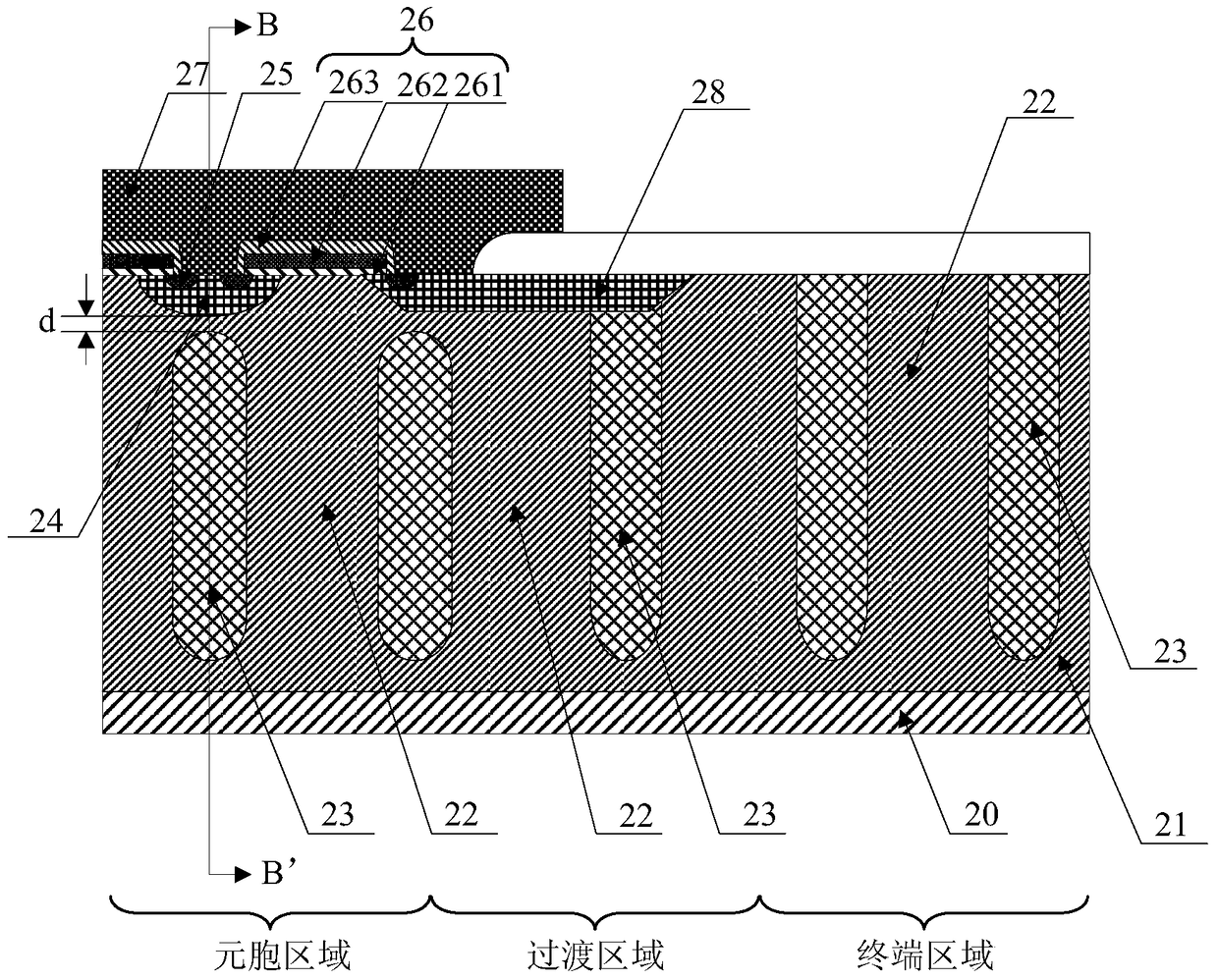

[0080] see Figure 2 to Figure 7 , the present invention provides a semiconductor device with a superjunction structure, the semiconductor device at least includes: a cell region; each of the cell regions includes a substrate 20, a first conductivity type on the substrate 20 The epitaxial layer 21, the guide post 22 of the first conductivity type and the guide post 23 of the second conductivity type located in the epitaxial layer 21 of the first conductivity type; the guide post 22 of the first conductivity type and the guide post 23 of the second conductivity type The guide pillars 23 extend in the epitaxial layer 21 of the first conductivity type along the direction of the current path, and are alternately connected and arranged in the direction perpendicular to the current path to form a super junction structure; the epitaxial layer 21 of the first conductivity type It also includes a first body region 24 of the second conductivity type and a source region 25 of the first c...

Embodiment 2

[0109] see Figure 8 to Figure 11, in this embodiment, a semiconductor device with a super junction structure is also provided, the semiconductor device at least includes: a cell region; the cell region includes a substrate 20, a first substrate located on the substrate 20 The epitaxial layer 21 of the conductivity type, the guide post 22 of the first conductivity type and the guide post 23 of the second conductivity type located in the epitaxial layer 21 of the first conductivity type; the guide post 22 of the first conductivity type and the guide post 23 of the second conductivity type Guide pillars 23 of two conductivity types extend in the epitaxial layer 21 of the first conductivity type along the direction of the current path, and are alternately connected and arranged in the direction perpendicular to the current path to form a super junction structure; The epitaxial layer 21 also includes a first body region 24 of the second conductivity type and a source region 25 of ...

Embodiment 3

[0125] see Figure 12 to Figure 13 , this embodiment also provides a semiconductor device with a super junction structure, the semiconductor device at least includes: a cell region; the cell region includes a substrate 20, a first conductive layer located on the substrate 20 epitaxial layer 21 of the first conductivity type, a guide post 22 of the first conductivity type and a guide post 23 of the second conductivity type located in the epitaxial layer 21 of the first conductivity type; the guide post 22 of the first conductivity type and the second Guide pillars 23 of conductivity type extend in the epitaxial layer 21 of the first conductivity type along the direction of the current path, and are alternately connected and arranged in the direction perpendicular to the current path to form a super junction structure; the epitaxial layers of the first conductivity type Layer 21 also includes a first body region 24 of the second conductivity type and a source region 28 of the fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More