Formation method of transistor

A transistor and substrate technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems affecting the performance of semiconductor devices, defects in semiconductor devices, etc., to achieve the effect of optimizing performance and reducing the number of traps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

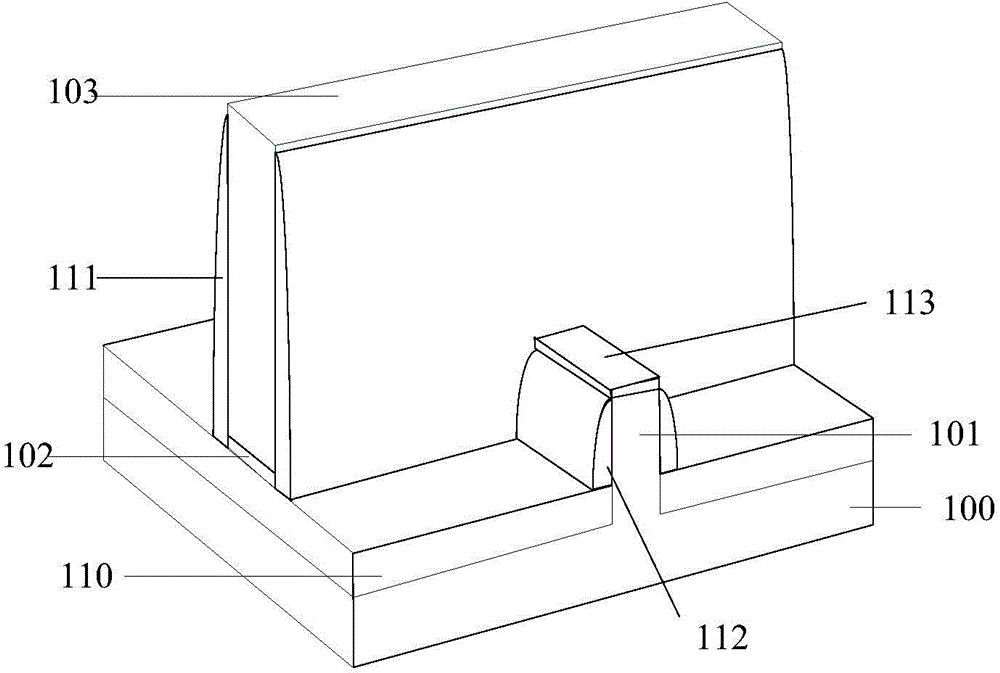

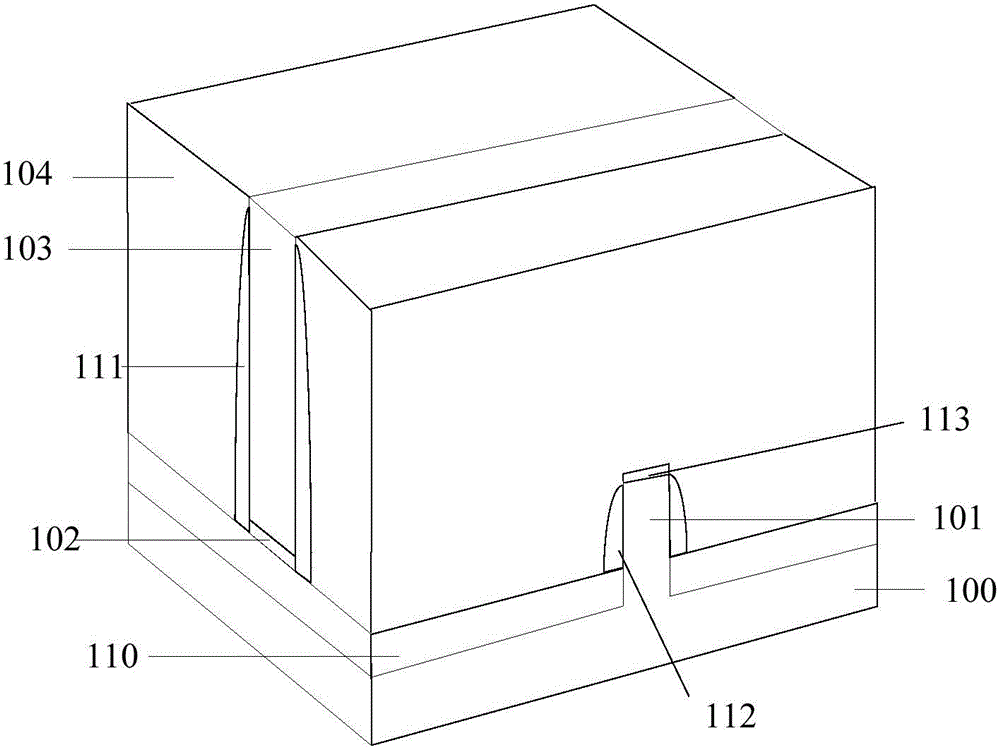

[0035] In the prior art, when the hafnium-based high-K material is used as the material of the gate dielectric layer, it is easy to generate defects in the semiconductor device, thereby affecting the performance of the semiconductor device. Analyzing the causes of defects in semiconductor devices, trap defects are prone to occur in hafnium-based high-K materials, and interface state defects are also prone to occur at the interface between hafnium-based high-K materials and silicon substrates. A silicon oxide layer is added between the high-K material and the silicon substrate to reduce interface state defects, but in actual production, problems such as increased leakage current and threshold voltage drift caused by interface state defects are still serious.

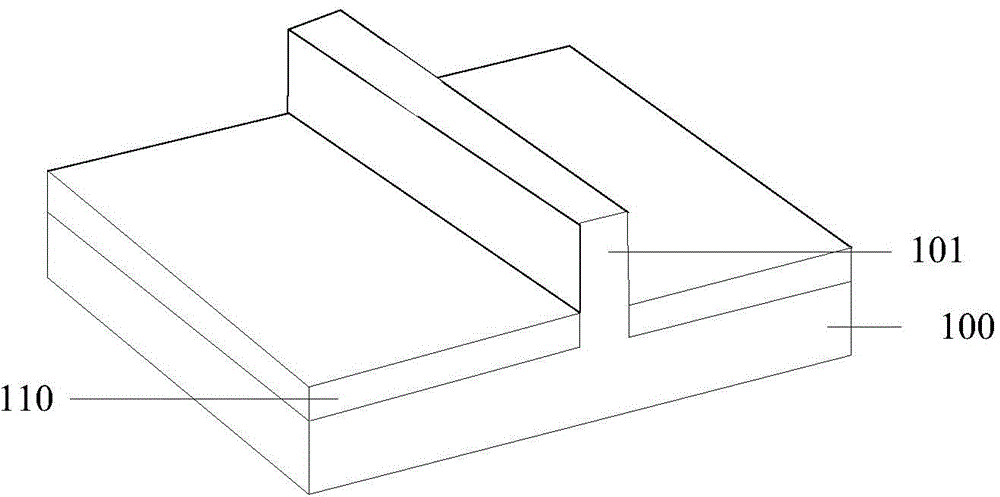

[0036] For this reason, the present invention provides a method for forming a transistor. In the method for forming a transistor of the present invention, a hafnium-based dielectric layer is formed at the bottom of the ope...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More