Formation method of semiconductor structure

A semiconductor and graphics layer technology, applied in the field of semiconductor structure formation, can solve the problems of semiconductor structure yield chip output, conduction performance, and contact resistance reduction, and achieves easy control of feature size and improved chip performance. Yield, uniformity improvement effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] It can be seen from the background art that the yield rate of the semiconductor structure formed in the prior art needs to be improved, and the output of chips is low.

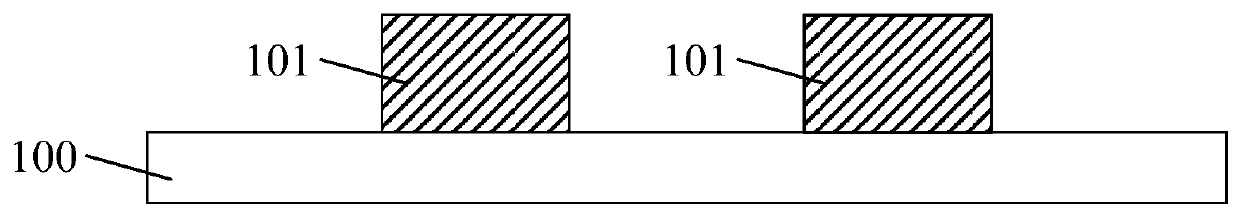

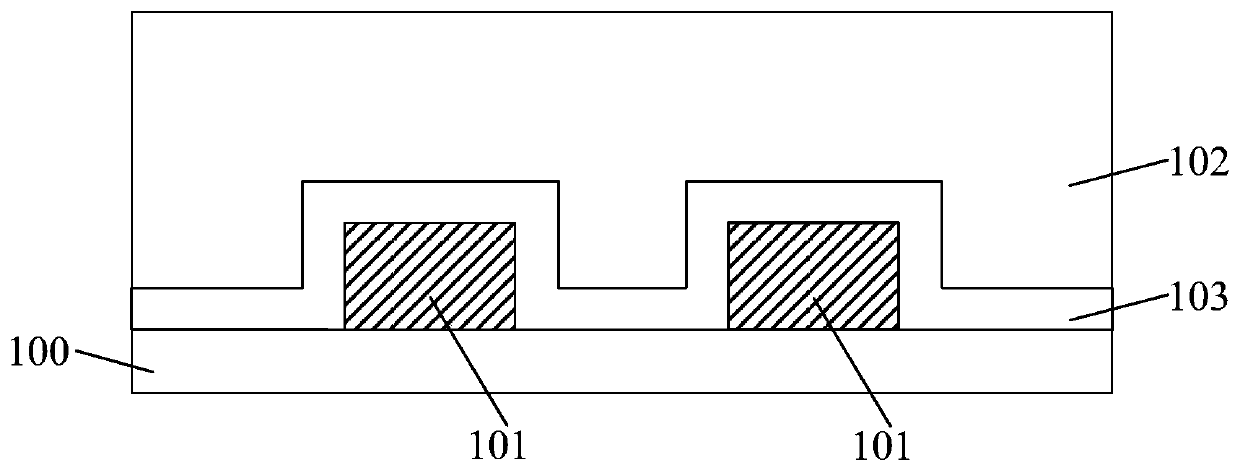

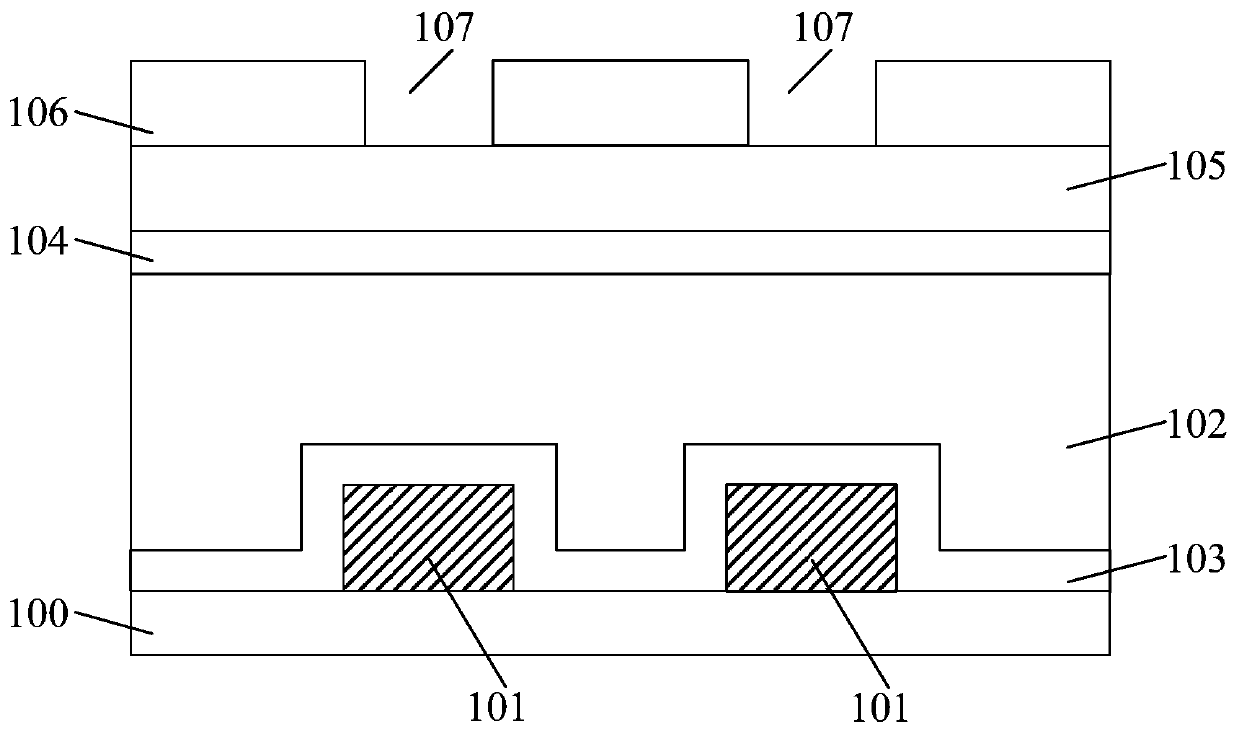

[0033]In one embodiment, the formation process of the semiconductor structure includes the following steps: step S1, providing a substrate, the substrate has an underlying metal layer, and forming a dielectric layer on the surface of the substrate; step S2, forming a pattern on the surface of the dielectric layer layer, the graphic layer has an opening exposing the surface of the dielectric layer; step S3, using the graphic layer as a mask, etching the dielectric layer along the opening until the surface of the underlying metal layer is exposed, and forming a contact in the dielectric layer hole; step S4, performing wet cleaning on the contact hole; step S5, forming a conductive layer filling the contact hole.

[0034] In the above methods, the dielectric layer is generally etched by a dry etching proce...

PUM

| Property | Measurement | Unit |

|---|---|---|

| contact angle | aaaaa | aaaaa |

| contact angle | aaaaa | aaaaa |

| relative permittivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More