Semiconductor device and forming method of semiconductor device

A semiconductor and device technology, applied in the field of semiconductor devices and their formation, can solve the problems of increased drain current, decreased gate threshold voltage, increased number of electrons, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

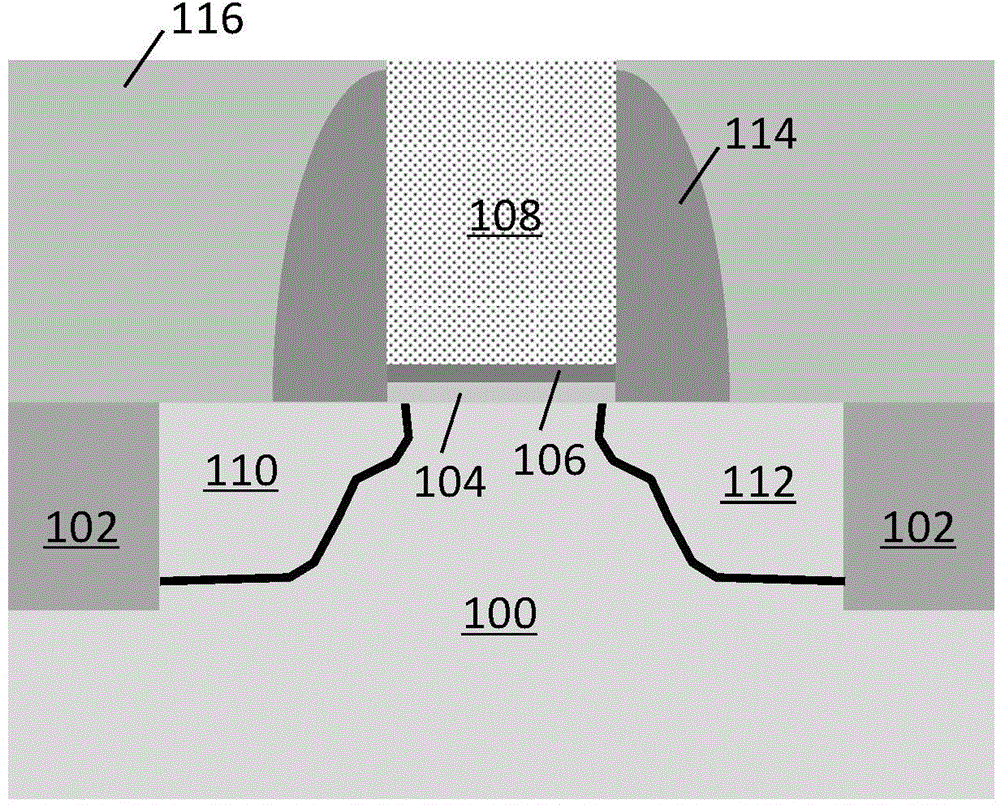

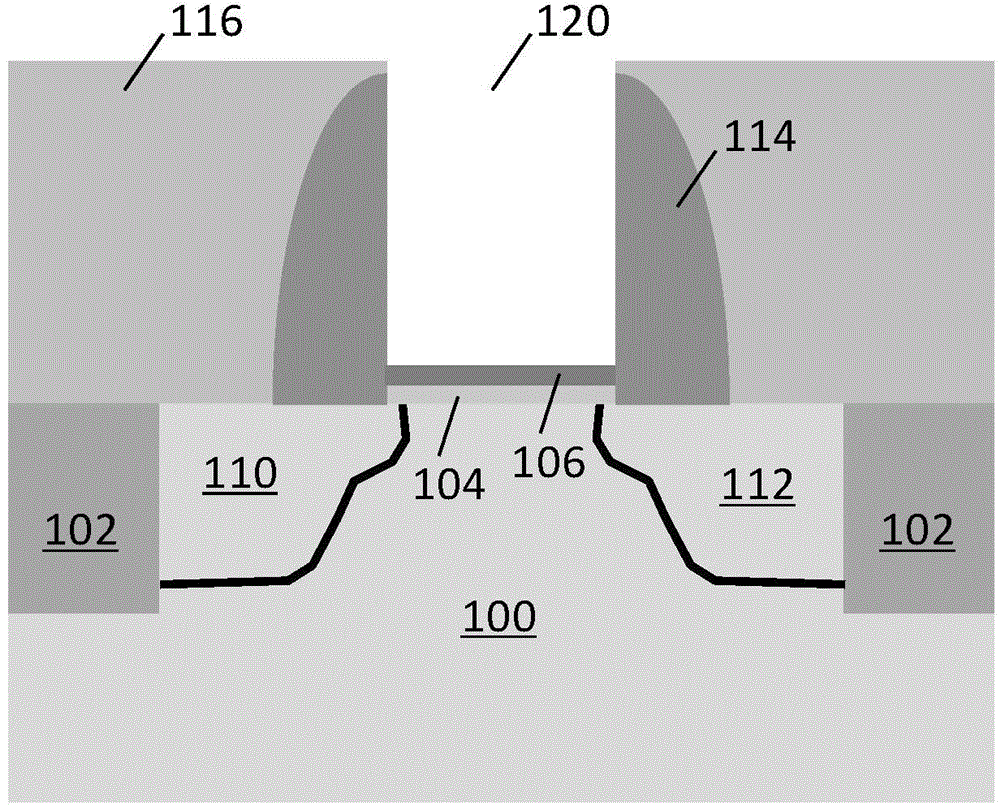

[0027] Embodiments of the present invention are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals designate the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary only for explaining the present invention and should not be construed as limiting the present invention.

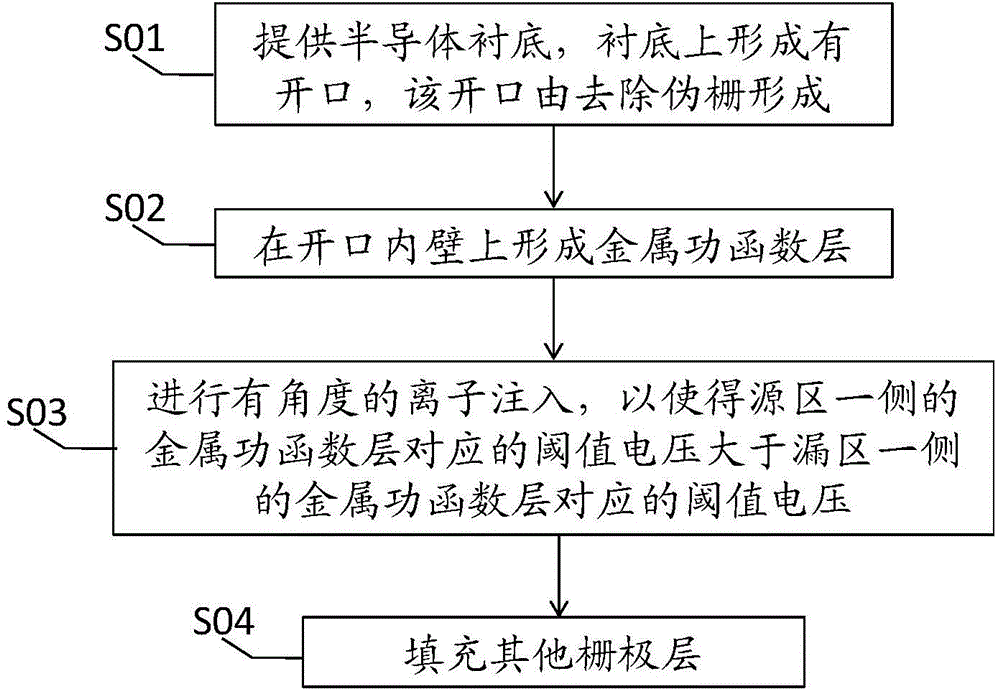

[0028] The present invention proposes a method for manufacturing a semiconductor device, referring to figure 1 As shown, it includes: providing a semiconductor substrate with an opening formed on the substrate, and the opening is formed by removing the dummy gate; forming a metal work function layer on the inner wall of the opening; performing ion implantation at an angle so that the metal on the side of the source region The threshold voltage corresponding to the work function layer is greater than the threshold voltage corresponding to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More