Digital correction method for array analog to digital converter of high-performance CMOS image sensor

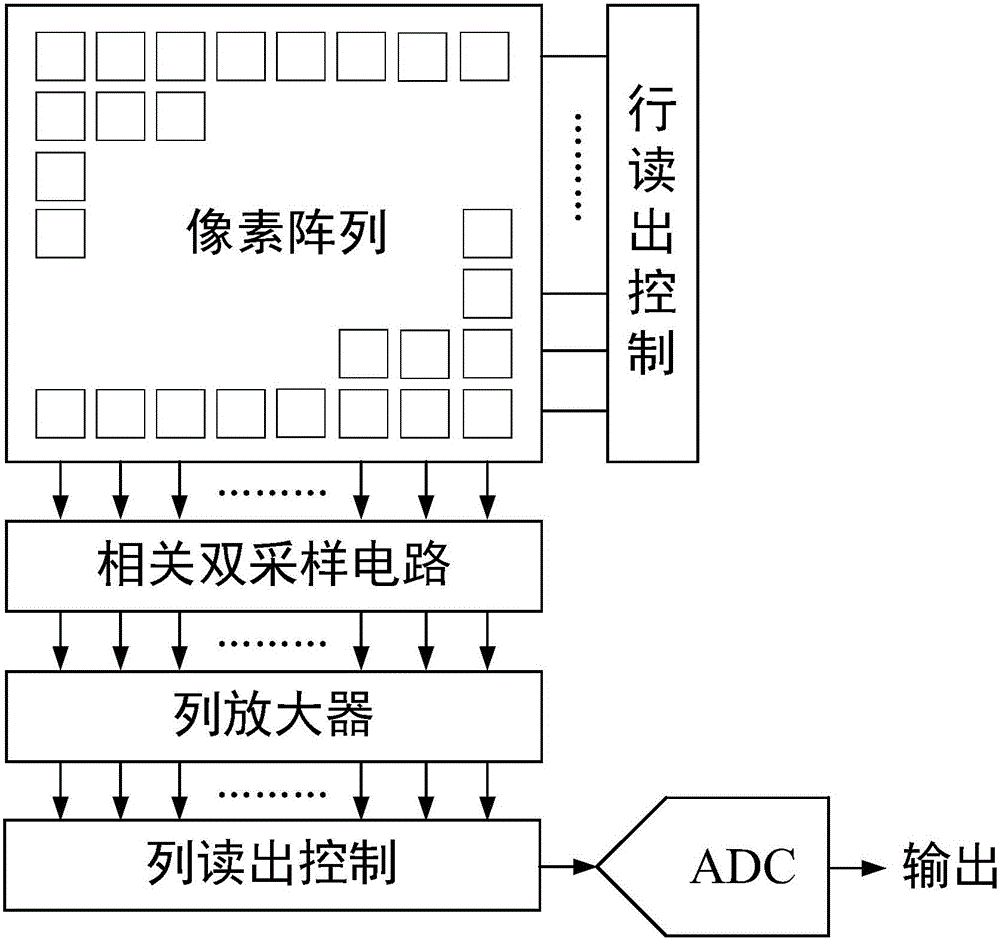

An image sensor and analog-to-digital converter technology, which is applied in image communication, color TV components, and TV system components to save chip area, reduce mismatch problems, and save area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

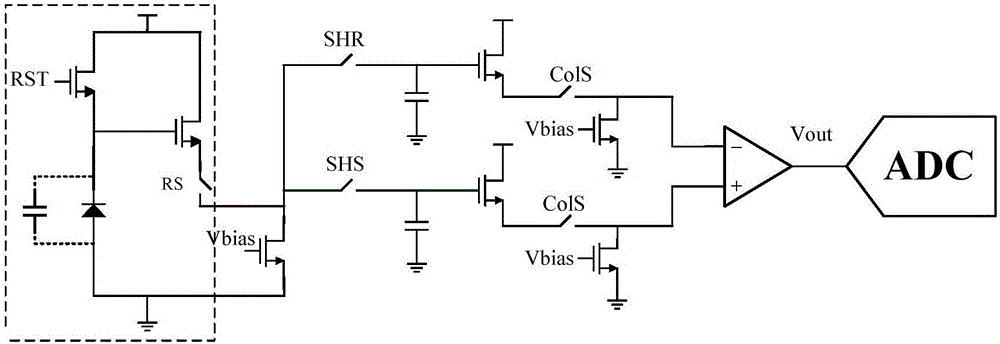

Method used

Image

Examples

Embodiment 1

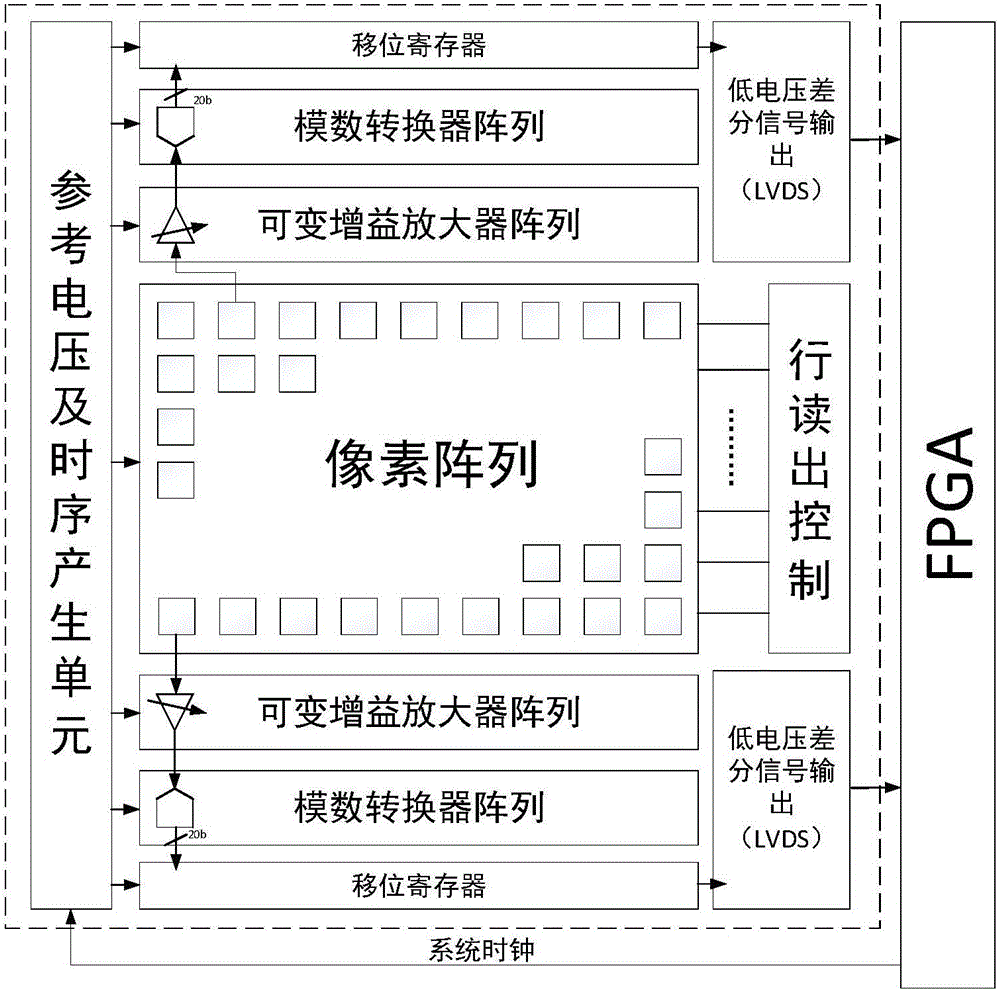

[0042] The digital correction method of the high-performance CMOS image sensor array analog-to-digital converter is as follows: N-channel ADCs on the CIS chip are arranged in an array. During normal operation, the data strobe (MUX) connects the sensor output with the ADC input. In the calibration stage, the data strobe connects the calibration signal to the ADC input, and the ADC output is connected to the off-chip in-circuit system programming (ISP) chip of the CIS through a low-voltage differential signal output (LVDS) high-speed interface. During the digital calibration process, the ADC The output first performs data recovery operation through the bit weight adjustment circuit, and then inputs it into the digital correction engine for correction operation, feeds back the corrected data to the bit weight adjustment circuit for bit weight correction, and then outputs the corrected data to the subsequent image signal processing module The circuit completes the following routine...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More